# A high-efficiency switching amplifier employing multi-level pulse width modulation

Jan Doutreloigne

**Abstract**—This paper describes a new multi-level switching amplifier concept, targeting increased power efficiency for analog signals with a very high crest factor. Interesting application fields include audio power amplifiers or line drivers in central-office ADSL and VDSL equipment. Calculations prove its superior power efficiency compared to conventional class-D switching amplifiers as well as linear class-AB and class-G amplifiers. A silicon implementation of a multi-level switching audio amplifier chip is currently in progress.

**Keywords**—Audio amplifier, multi-level architecture, power efficiency, pulse width modulation, self-oscillating amplifier, switching amplifier.

#### I. INTRODUCTION

Linear class-AB amplifiers are undoubtedly the most obvious choice when analog signals have to be handled with a high degree of accuracy. There are, however, certain applications where these linear class-AB amplifiers suffer from a very poor power efficiency due to the high crest factor (defined as the ratio of the peak value to the rms value) of the analog signal. Typical examples are audio signals or ADSL/VDSL signals, which normally behave like a "noisy" low-amplitude signal with sporadic high-amplitude peaks or bursts. While the supply voltage is determined by the high-amplitude part of the signal in order to preserve signal purity over the whole dynamic range, the average power efficiency will predominantly depend on the low-amplitude part of the signal, resulting in disappointingly low values of the efficiency, typically in the range from 10% to 15%. An interesting approach to solve this problem is to use switching amplifiers instead. Since the output transistors in switching amplifiers no longer act as linear amplifying components but merely as solid-state switches, the power efficiency can be increased considerably. This paper presents an original type of switching amplifier, aiming at maximum power efficiency for analog signals with a very high crest factor.

Jan Doutreloigne is with the Centre for Microsystems Technology (CMST), affiliated to the Interuniversity Microelectronics Centre (IMEC) and the University of Gent, building iGent, Technologiepark 15, 9052 Zwijnaarde, Belgium (phone: +32-(0)9-264-53-56; fax: +32-(0)9-264-35-94; e-mail: jan.doutreloigne@ugent.be).

#### II. AMPLIFIER ARCHITECTURE

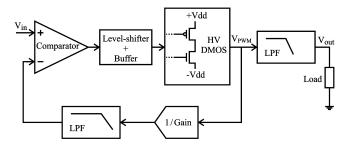

The best known switching amplifier is the class-D amplifier, also often referred to as a class-S amplifier. A basic single-ended version of such a class-D switching amplifier is shown in Fig. 1. The binary high-voltage output signal is fed back through an attenuator and low-pass filter before being compared to the analog input signal. The comparator then decides which of the 2 output transistors should be activated in an attempt to compensate the detected difference between the fed-back output signal and the analog input signal. When the control loop is properly designed, it turns out that this circuit behaves like a self-oscillating switching amplifier in which the binary output signal V<sub>PWM</sub> represents a Pulse-Width-Modulated (PWM) approximation of the amplified analog input signal, while the oscillation frequency depends on the loop dynamics, mainly the low-pass loop filter characteristics. Sending this binary output signal through a low-loss LC low-pass filter, having a cut-off frequency well below the switching frequency, will produce the desired amplified analog signal into the load [1].

Fig. 1 block diagram of a single-ended class-D switching amplifier

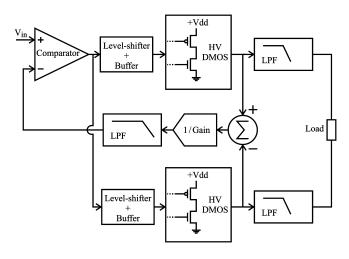

There are of course numerous variations to the circuit of Fig. 1. Some of them are synchronized to a fixed-frequency clock signal instead of relying on the asynchronous self-oscillating behavior of the amplifier in Fig. 1. Other implementations employ a balanced output configuration instead of a single-ended one. Fig. 2 depicts a balanced alternative to the circuit of Fig. 1, exhibiting improved linearity as the even harmonics of the switching frequency are very effectively suppressed in a perfectly symmetrical architecture. Another advantage of a balanced configuration is that the supply voltage can be halved for a given signal amplitude.

Although the switching amplifiers from Fig. 1 and Fig. 2 offer excellent power efficiency from a theoretical point of view,

ISSN: 1998-4480

reality can be quite different. The binary output signal is constantly switching with high amplitude (between -Vdd and +Vdd in the circuit of Fig. 1, or between ground and +Vdd in the circuit of Fig. 2), resulting in a strong output current component at switching frequency. The high amplitude of this output current component, determined by the input impedance of the low-loss LC low-pass filter, will produce considerable power dissipation in the output transistors due to their non-zero on-state resistance. For analog signals with a very high crest factor, this dissipation in the output transistors can be much more important than the average useful signal power in the load, yielding rather low values of power efficiency. Also the significant dynamic power losses, caused by the continuous charging and discharging of parasitic capacitances at high switching frequency and high switching amplitude, have a negative impact on the global power efficiency. Both effects make very clear that the power efficiency can only be improved by reducing the amplitude of the switching output signal. However, in order to maintain the necessary dynamic range for the analog signal with high crest factor, the switching levels of the output stage must be made adjustable to the instantaneous signal amplitude. The resulting circuit is a multi-level switching amplifier.

Fig. 2 block diagram of a balanced class-D switching amplifier

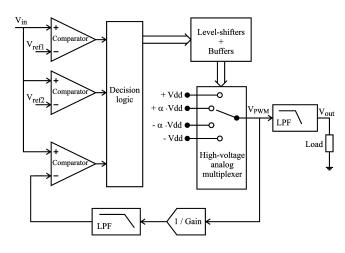

Very few examples of multi-level switching amplifiers can be found in literature. They employ a multi-cell architecture based on the "flying battery" concept, where rechargeable batteries or "super capacitors" are needed to power the series connection of several switching cells [2]. In contrast to those very sophisticated designs, this paper proposes a less complex alternative architecture, employing fixed supply voltages instead of "flying batteries". A simplified block diagram of this novel multi-level switching amplifier is depicted in Fig. 3. This amplifier is also based on the self-oscillating principle as in the class-D switching amplifier of Fig. 1, but this time the classic binary push-pull output stage has been replaced by a 4-input multiplexer, consisting of 4 bidirectional high-voltage analog switches that can be implemented as symmetrical DMOS devices. This high-voltage analog multiplexer produces a

4-level PWM approximation of the analog input signal. An important logic block in the circuit decides between which of the 4 supply voltage levels the multiplexer should switch in order to minimize the power losses. To that purpose, a set of comparators constantly monitors the instantaneous input signal strength. When the signal amplitude is very low, the decision logic selects the supply voltages  $-\alpha \cdot Vdd$  and  $+\alpha \cdot Vdd$ , the fraction  $\alpha$  being a number much smaller than 1. When the comparators detect a high signal strength, on the other hand, the decision logic will bring the supply voltages -Vdd and +Vdd into action. One could say that this novel multi-level switching amplifier resembles a discrete version of the linear class-G amplifier, which is basically a linear class-AB amplifier where the output stage is powered by a much lower supply voltage when the input signal shows low amplitudes.

Fig. 3 block diagram of a multi-level switching amplifier

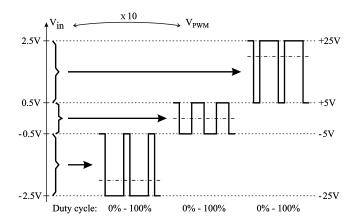

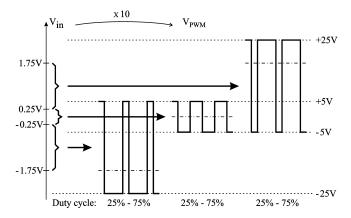

There are still several options regarding the operation of the decision logic. From the point of view of power consumption, the switching strategy illustrated in Fig. 4 is undoubtedly the best choice (for typical values of Vdd = 25V,  $\alpha$  = 0.2, and an amplifier gain of 10).

Fig. 4 basic switching strategy for a multi-level switching amplifier

Depending on the signal strength, the decision logic always selects the supply voltages that result in minimum switching amplitude. There is, however, an important drawback: When the

ISSN: 1998-4480

input signal passes one of the comparator reference levels, the duty ratio of the switching output signal suddenly changes from 0 to 100%, or vice versa. Detailed circuit simulations have shown that this results in improper behavior of the self-oscillating loop. As a consequence, the accuracy of the filtered output signal in the load deteriorates significantly. It is therefore advisable to use the improved switching strategy of Fig. 5 instead. At high signal strength, the switching amplitude is somewhat larger than in the case of Fig. 4, yielding a slightly reduced power efficiency, but for the chosen circuit parameters the duty ratio no longer leaves the 25% to 75% range, no matter what the instantaneous input signal amplitude may be. The feedback loop now operates properly within the whole dynamic range, and therefore, the switching strategy of Fig. 5 is definitely the best trade-off between power efficiency and signal purity.

Fig. 5 improved switching strategy for a multi-level switching amplifier

# III. POWER EFFICIENCY CALCULATION

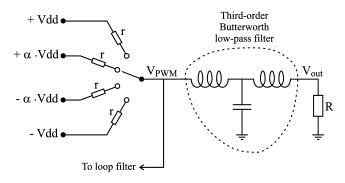

In order to estimate the power efficiency of the multi-level switching amplifier and to allow a comparison with other amplifier types, the simplified model of Fig. 6 will be used for the high-voltage analog multiplexer in the output stage of the amplifier.

Fig. 6 simplified model of the high-voltage analog multiplexer to calculate the power efficiency of a multi-level switching amplifier

Each bidirectional analog switch in the multiplexer is modeled by a small resistor with value r, representing the on-state resistance of the symmetrical DMOS devices. In that way, we can fairly easily calculate the power losses caused by the switching current flowing through the DMOS transistors. It is important to note that the dynamic power losses, caused by the continuous charging and discharging of parasitic capacitances, will be neglected in this analysis.

Assuming that a DC input signal is applied to the amplifier, the switching output signal  $V_{PWM}$  can be written as follows:

$$V_{PWM}(t) = V_{DC} + \sum_{n=1}^{\infty} a_n \cdot \cos\left(\frac{2\pi nt}{T_S}\right)$$

In this expression, the first term corresponds to the amplified DC signal in the load resistance R, while the second term represents the Fourier series of the AC part in the switching waveform,  $T_s$  being the switching period. Knowing that in a real circuit implementation the on-state resistance r of the DMOS switches should be much smaller than the load resistance R, we can say in a first-order approximation that  $V_{PWM}$  will be switching between supply voltage levels  $V_A$  and  $V_B$ , where the precise values of  $V_A$  (–Vdd or – $\alpha$ -Vdd) and  $V_B$  (+ $\alpha$ -Vdd or +Vdd) are selected by the decision logic according to the switching strategy of Fig. 5. The Fourier coefficients are then given by the formula:

$$a_n = \frac{2(V_B - V_A)}{\pi n} \cdot \sin\left(\frac{\pi n \tau}{T_S}\right) \; ; \quad n = 1, \dots, \infty$$

The pulse duration  $\tau$  will depend on the input signal strength and the selected supply voltage levels according to the following expression for the duty ratio of  $V_{PWM}$ :

$$\frac{\tau}{T_S} = \frac{V_{DC} - V_A}{V_B - V_A}$$

This leads to a very good first-order approximation for the total average power dissipation in the bidirectional switches in the high-voltage analog multiplexer:

$$\overline{P_{r,tot}} = r \cdot \left(\frac{V_{DC}}{R}\right)^2 + \frac{r}{2} \cdot \sum_{n=1}^{\infty} \frac{a_n^2}{|Z_{in}(n\omega_s)|^2}$$

The first term represents the effect of the DC current flowing from the multiplexer to the load, while the second term reflects the effect of the switching current. The amplitudes of the harmonics in this switching current depend on the amplitudes of the corresponding harmonics in the  $V_{PWM}$  waveform as well as on the input impedance of the low-loss LC low-pass filter. In case a third-order Butterworth low-pass filter is adopted, this input impedance is given by:

ISSN: 1998-4480

$$\left|Z_{in}(\omega)\right|^{2} = R^{2} \cdot \frac{1 + \left(\frac{\omega}{\omega_{c}}\right)^{6}}{1 + \frac{4}{9} \cdot \left(\frac{\omega}{\omega_{c}}\right)^{2} + \frac{4}{9} \cdot \left(\frac{\omega}{\omega_{c}}\right)^{4}}$$

The angular cut-off frequency  $\omega_c$  should of course be chosen much below the angular switching frequency  $\omega_s$ . We now define the power efficiency  $\eta$  as the ratio between the useful DC output power in the load and the total power delivered by all supply voltages to the multiplexer and the load:

$$\eta = \frac{P_R}{P_R + \overline{P_{r,tot}}} = \frac{\frac{V_{DC}^2}{R}}{\frac{V_{DC}^2}{R} + \overline{P_{r,tot}}}$$

This leads to the following expression for calculating the power efficiency in the multi-level switching amplifier:

$$\eta = \frac{1}{1 + \frac{r}{R} + \frac{r \cdot R}{2V_{DC}^2} \cdot \sum_{n=1}^{\infty} \frac{a_n^2}{\left|Z_{in}(n\omega_S)\right|^2}}$$

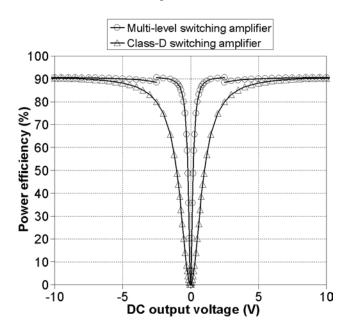

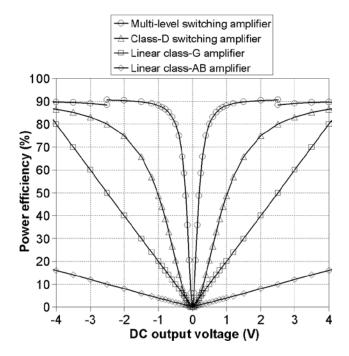

Some interesting results, based on these formulas, are gathered in Figs. 7, 8 and 9. These data correspond to the following system parameters: Vdd = 25V ,  $\alpha$  = 0.2 , gain = 10 , R =  $10 \cdot r$  ,  $\omega_s$  =  $5 \cdot \omega_c$  . Fig. 7 compares the power efficiency of the multi-level switching amplifier and the class-D switching amplifier, the latter employing exactly the same system parameters except for the fact that the supply voltage levels of  $-\alpha \cdot Vdd$  and  $+\alpha \cdot Vdd$  are not present of course.

Fig. 7 power efficiency: comparison between multi-level and class-D switching amplifiers under DC excitation

At small signal levels, which is the most important part when the amplifier is intended for signals with a very high crest factor, the superior performance of the multi-level switching amplifier is very clear. At 1V output voltage, the multi-level switching amplifier exhibits 88% efficiency against 49% for the class-D switching amplifier! At 2V output voltage, the difference is still 90% against 75%. At higher signal levels, the difference almost disappears because the effect of the switching current, having a smaller amplitude in the multi-level version, becomes negligible compared to the effect of the DC current, which is exactly the same in both switching amplifiers. Also note the small discontinuity at 2.5V output voltage for the multi-level switching amplifier due to the change in one of the supply voltages that are selected by the decision logic according to the switching strategy of Fig. 5.

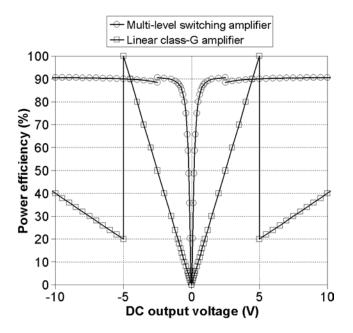

Fig. 8 compares the performance of the multi-level switching amplifier and an ideal linear class-G amplifier, the latter employing exactly the same 4 supply voltage levels. This time the performance of the multi-level switching amplifier is superior over the whole range, except for output voltage levels in the neighborhood of –5V and +5V, when the linear class-G amplifier operates very close to the  $-\alpha$ ·Vdd and  $+\alpha$ ·Vdd supply voltages.

Fig. 8 power efficiency: comparison between a multi-level switching amplifier and an ideal linear class-G amplifier under DC excitation

Finally, Fig. 9 compares the power efficiency of all relevant linear and switching amplifiers in the range of small signal levels. From this graph it's clear that the multi-level switching amplifier is definitely the best choice when it comes to amplifying analog signals with a very high crest factor!

Fig. 9 power efficiency: comparison between different types of switching and linear amplifiers under DC excitation

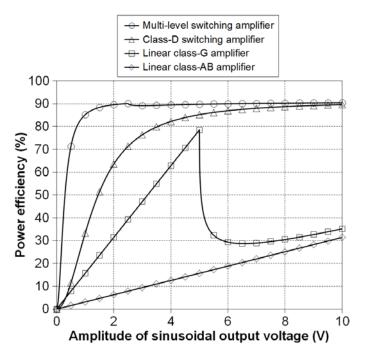

Note that the formula for calculating the power efficiency in the multi-level switching amplifier was derived for pure DC excitation of the amplifier. When other types of input signals are considered (sine wave, audio, xDSL,...), the global power efficiency can be estimated by repeating a similar calculation using the probability density function of the signal under consideration. Such a quasi-static approximation implies that the switching frequency is much higher than the signal bandwidth, which is normally the case in switching amplifiers. Fig. 10 compares again the power efficiency of all relevant linear and switching amplifiers, but this time for the particular case of sinusoidal excitation of the amplifier. Obviously, the same conclusion can be drawn from this graph: the multi-level switching amplifier has definitely the best performance, especially at very low signal levels, which is crucial when it comes to amplifying analog signals with a very high crest factor!

### IV. INITIAL CIRCUIT SIMULATIONS

In order to verify the theoretical calculations, a first version of a multi-level switching amplifier according to the architecture of Fig. 3 and the improved switching strategy of Fig. 5 was designed in the 50V  $0.35\mu m$  I3T50 smart power technology of ON Semiconductor. The targeted application in this design was a monolithically integrated 2W audio amplifier with 20kHz bandwidth.

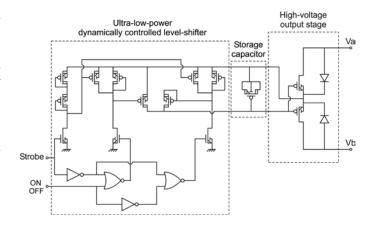

For the bidirectional high-voltage analog switches in the 4-level multiplexer the sophisticated circuit of Fig. 11 was used. The actual switch consists of the 2 symmetrically coupled p-type DMOS transistors between the nodes  $V_a$  and  $V_b$ , while the gate electrodes of those 2 DMOS transistors are driven by a dynamically controlled level-shifter to keep the additional

power losses in the driving circuit to an absolute minimum. These ultra-low-power level-shifters were originally designed for driving high-voltage bistable LCDs [3,4], but are equally well suited for this audio amplifier application.

Fig. 10 power efficiency: comparison between different types of switching and linear amplifiers under sinusoidal excitation

Fig. 11 bidirectional high-voltage analog switch driven by a dynamically controlled level-shifter

The system parameters in the design of the multi-level switching audio amplifier were as follows: Vdd = 25V,  $\alpha$  = 0.2, gain = 10, R = 100 $\Omega$ , r = 10 $\Omega$ , f<sub>s</sub> = 100kHz, f<sub>c</sub> = 20kHz.

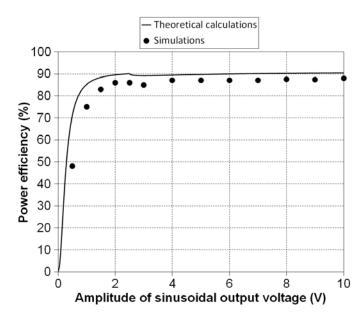

The designed circuit was extensively simulated using Spectre and some of the obtained simulation data are gathered in Fig. 12. It shows the simulated power efficiency in the particular case of a sinusoidal signal of 1kHz frequency with variable amplitude. Note that all power losses are taken into account during the simulation, including the dissipation in the level-shifters of the bidirectional high-voltage analog switches and all other control circuitry.

When comparing the simulated data with the previously described theoretical predictions (also plotted in the same graph of Fig. 12), it is seen that the simulated power efficiency is somewhat lower than the calculated one. This is partially due to the power losses in the level-shifters and all other control circuitry, but it can also be attributed to the dynamic switching losses caused by the continuous charging and discharging of the parasitic capacitances in the multiplexer switches at high frequency ( $f_s = 100 \text{kHz}$ ). Nevertheless, these simulation results reveal excellent performance of the multi-level switching amplifier in terms of power efficiency!

Fig. 12 power efficiency: comparison between theoretical calculations and circuit simulations for a multi-level switching amplifier under 1kHz sinusoidal excitation

## V. REAL SILICON IMPLEMENTATION

As the initial circuit simulations prove very promising, the proposed multi-level switching amplifier concept will soon be implemented in a real audio amplifier ASIC. This IC design will be submitted to the MPW (Multi-Project Wafer) service of Europractice for integration in the 50V 0.35 $\mu$ m I3T50 smart power technology of ON Semiconductor.

### VI. CONCLUSION

A novel multi-level switching amplifier concept, aiming at improved power efficiency for analog signals with a very high crest factor, was presented. Calculations have proven its superior performance in terms of power efficiency compared to conventional class-D switching amplifiers as well as linear class-AB and class-G amplifiers. This new concept is currently being implemented in a highly efficient audio amplifier chip.

#### REFERENCES

- V. De Gezelle, J. Doutreloigne, and A. Van Calster, "A 765mW high-voltage switching ADSL line-driver," *Solid-State Electronics*, vol. 49, no. 12, pp. 1947-1950, 2005.

- [2] H. Ertl, J. W. Kolar, and F. C. Zach, "Analysis of a multilevel multicell switch-mode power amplifier employing the "flying-battery" concept," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 816-823, 2002.

- [3] J. Doutreloigne, H. De Smet, and A. Van Calster, "A versatile micropower high-voltage flat-panel display driver in a 100V 0.7μm CMOS Intelligent Interface Technology," *IEEE Journal of Solid-State Circuits*, vol. 36, no. 12, pp. 2039-2048, 2001.

- [4] J. Doutreloigne, "A monolithic low-power high-voltage driver for bistable LCDs," *Microelectronics Journal*, vol. 37, no. 11, pp. 1220-1230, 2006.