# A Review of Commutation Problem in Matrix Converter

Farshad Soltanian Department of Electrical and Computer Engineering

Isfahan University of Technology Isfahan, Iran f.soltanian@ec.iut.ac.ir

Abstract—Matrix converters have attractive features including their high density power and bidirectional power flow. One of the challenges of matrix converter is commutation problem. Commutation problem in matrix converter is more complex than other common converters such as AC-DC-AC converters because there isn't any natural free - wheeling path in matrix converters. In this article, different commutation methods have been considered and compared with each other such as current sign based commutation which is a base method in these converters, voltage based commutation that decreases commutation time and improved the waveforms ,and commutation circuits that it has different circuits itself that they don't need to determine the sign of current. The simulation of two methods have been proposed and compared with each other.

Keywords—matrix converter, commutation, bidirectional switches

# I. INTRODUCTION

By increasing the industrial power converting, the need of bidirectional power flow between AC side and load side is perceived. Some applications such as roll, conveyor, and elevators can be mentioned. In these applications, a lot of energy can be saved by returning the extra energy at the load side to AC side. Another important application for bidirectional power flow is renewable energy application in wind farms. So, AC/AC converters can be used for transmitting power in both directions. AC/AC converters are classified into two groups including direct converters and indirect converters. Indirect converters convert AC voltage to DC and then convert it to AC again. In these converters, DC link is necessary that is one the limitations of these converters. Direct converters are classified into phase control and forced commutation converters. Phase control direct converters are cycloconverters and force commutation direct converters are matrix converters.

Desirable features of matrix converters are:

• Simple and compact power circuit

- Producing load voltage with desire amplitude and frequency

- Operating in unity power factor is possible

- Sinusoidal input and output currents

These ideal features can be performed by matrix converters and this is a reason to be interested in these converters. Matrix converter is arranged by bidirectional controlled switches as the main power elements to produce output voltage of the system without frequency limitation. This converter doesn't have any DC link and doesn't need any bulky energy storage element. Matrix converter is very attractive and it has the above interesting features but the commutation problem is a challenge in them yet. Different multi step methods are proposed for matrix converters that four-step commutation is one of the most acceptable methods between all of the methods. Technical problems of multi-step methods are including: 1) The sequence of turning on and off the switches is depended on the output current sign and/or the amplitude of the involved input voltages in commutation and the reliability of the commutation is depended on accurate measurement of voltages and/or current sign determination. When the amplitude of the voltages or currents is small, the commutation may be gotten error. 2) Decreasing commutation time increases the quality of input and output waveforms. This task can be done by reducing the steps of commutation.

In this article, four-step commutation based on current sign detection has been presented. Other methods that are based on measuring voltage amplitude have been presented. At the end, to decrease the commutation time, commutation circuits have been introduced. These circuits can be used in aerospace applications, because these applications need a short time of commutation.

As we know, the advantages in semiconductors have an important role in developing the equipment and applications of power conversions. Of the important purposes in designing of power electronic equipment is increasing the continuity of power density. So, at the end of this article, a new power key has been introduced that can solve many problems in the commutation of matrix converters.

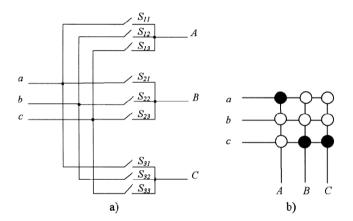

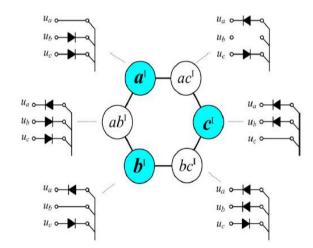

## A. Matrix Converter Structure

A matrix converter is included by 9 bidirectional switches which placed in 3 groups that each group is consisted of 3 switches and each group is related to each phase. The arrangement of these switches which connect the lines a, b and c to lines A, B and C has been shown in Fig. 1. A bidirectional switch can control the current in both directions.

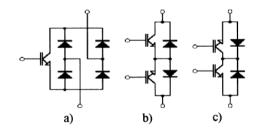

# B. Bidirectional Switches Operation analysis

Bidirectional switches are the main part of matrix converter. Practically, accessible unidirectional switches are used to make bidirectional switches. There are 3 methods to do this including: unidirectional switches, There are 3 methods to do emitter unidirectional switches, two common collector unidirectional switches that are shown in Fig. 2. The first circuit needs just one gate driver and one active switch that is the easiest between two other circuits. This configuration has more losses because the current path is included two diode and one IGBT and because of hard commutation, the switching losses is high. But in two other cases, the losses is lower because the current path is included one diode and one IGBT and the commutation is soft.

Fig. 1. Arrangement of a matrix converter [2]

Fig. 2. Bidirectional switches [2]

# **III. COMMUTATION METHODS**

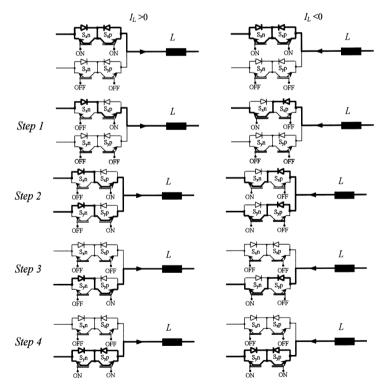

# A. Four Step Commutation Based on Current Sign Detection

In this method, the effort is not to flow wheeling current and overlap commutation is done, then. So the overcurrent is eliminated and semisoft commutation will be performed that means the half process of key commutation will be done naturally. Fig. 3 depicts the stages of this commutation method. The stages of this method are including:

- Turn off the off-going key that doesn't conduct. In this condition, the sign of the current can't change.

- Turn on the on-going key. Now, there is a unidirectional connection between input lines but wheeling current won't be occurred.

- Turn off the off-going key that conducted. In this moment, because of hard commutation, the current is forced to path from on-going key, not off-going key.

- Turn on the on-going key that doesn't conduct. This action is done to create four quadrant conditions for AC key and the ability of current sign changing.

## B. Conventional VBC (Mentzi Commutation)

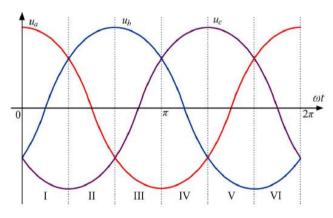

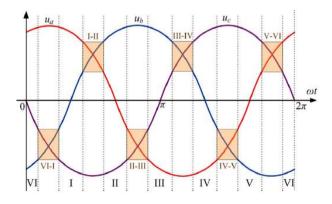

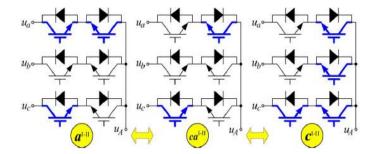

Mentzi commutation divides an input voltage fundamental cycle into 6 intervals (I, II, ...., IV), that shown in Fig. 4. In each interval, one input phase has the highest voltage, one phase has the lowest voltage, and another one has the middle voltage. Consider the  $3\emptyset/1\emptyset$  matrix converter, there are three main switching states and three commutation switching states in each interval.

Fig. 3. Four step commutation based on current sign detection [2]

In each main state, one of the input phases is bidirectionally connected to the load, and commutation states are intermediate states for two-step commutation. In each main state, the maximum unidirectional switches are turned on, these unidirectional switches will not cause a short circuit of input phases and can provide a freewheeling path for the load current in the commutation process. The main and commutation states of 6 intervals are presented in tables I and II. If there need a commutation from one main state to another main state, two steps are required:

- Turning off the unidirectional switches that are not necessary in target state.

- Turning on the unidirectional switches that are necessary in target state.

In Fig. 5, commutation state in interval I is shown and there isn't necessary any short circuit or open circuit. Mentzi commutation is valid when the amplitudes of input voltages are clear and can be measured easily. The problem is occurred when we are in some intervals that two voltages are close and similar to each other.

Fig. 4. Intervals of Mentzi commutation method [1]

Fig. 5. Two-step VBC commutation in interval I [1]

TABLE I. MAIN SWITCHING STATES IN NORMAL INTERVALS

| Normal intervals | Relative<br>voltage | Main<br>state           | SaAf | SaAr | S <sub>bAf</sub> | S <sub>bAr</sub> | $S_{cAf}$ | S <sub>cAr</sub> |

|------------------|---------------------|-------------------------|------|------|------------------|------------------|-----------|------------------|

|                  |                     | a <sup>I</sup>          | 1    | 1    | 1                | 0                | 1         | 0                |

| Ι                | $u_a > u_b > u_c$   | <b>b</b> <sup>I</sup>   | 0    | 1    | 1                | 1                | 1         | 0                |

|                  |                     | $c^{\mathrm{I}}$        | 0    | 1    | 0                | 1                | 1         | 1                |

|                  |                     | a <sup>II</sup>         | 1    | 1    | 0                | 1                | 1         | 0                |

| II               | $u_b > u_a > u_c$   | <b>b</b> <sup>II</sup>  | 1    | 0    | 1                | 1                | 1         | 0                |

|                  |                     | $c^{II}$                | 0    | 1    | 0                | 1                | 1         | 1                |

|                  |                     | a <sup>111</sup>        | 1    | 1    | 0                | 1                | 0         | 1                |

| III              | $u_b > u_c > u_a$   | <b>b</b> <sup>III</sup> | 1    | 0    | 1                | 1                | 1         | 0                |

|                  |                     | $c^{III}$               | 1    | 0    | 0                | 1                | 1         | 1                |

|                  |                     | a <sup>IV</sup>         | 1    | 1    | 0                | 1                | 0         | 1                |

| IV               | $u_c > u_b > u_a$   | <b>b</b> <sup>IV</sup>  | 1    | 0    | 1                | 1                | 0         | 1                |

|                  |                     | $c^{\rm IV}$            | 1    | 0    | 1                | 0                | 1         | 1                |

|                  |                     | a <sup>V</sup>          | 1    | 1    | 1                | 0                | 0         | 1                |

| V                | $u_c > u_a > u_b$   | <i>b</i> <sup>∨</sup>   | 0    | 1    | 1                | 1                | 0         | 1                |

|                  |                     | $c^{\vee}$              | 1    | 0    | 1                | 0                | 1         | 1                |

|                  |                     | a <sup>VI</sup>         | 1    | 1    | 1                | 0                | 1         | 0                |

| VI               | $u_a > u_c > u_b$   | b <sup>VI</sup>         | 0    | 1    | 1                | 1                | 0         | 1                |

|                  |                     | $c^{VI}$                | 0    | 1    | 1                | 0                | 1         | 1                |

TABLE II. COMMUTATION SWITCHING STATES IN CRITICAL INTERVALS

| Normal intervals | Relative<br>voltage | Main<br>state    | SaAf | SaAr | $S_{bAf}$ | S <sub>bAr</sub> | S <sub>cAf</sub> | S <sub>cAr</sub> |

|------------------|---------------------|------------------|------|------|-----------|------------------|------------------|------------------|

| intervais        | voltage             |                  | 0    | 1    | 1         | 0                | 1                | 0                |

| -                |                     | $ab^{I}$         | 0    | I    | 1         | 0                | I                | 0                |

| I                | $u_a > u_b > u_c$   | $bc^{I}_{I}$     | 0    | 1    | 0         | 1                | 1                | 0                |

|                  |                     | ca <sup>I</sup>  | 0    | 1    | 0         | 0                | 1                | 0                |

|                  |                     | $ab^{II}$        | 1    | 0    | 0         | 1                | 1                | 0                |

| Π                | $u_b > u_a > u_c$   | $bc^{II}$        | 0    | 0    | 0         | 1                | 1                | 0                |

|                  |                     | $ca^{II}$        | 0    | 1    | 0         | 1                | 1                | 0                |

|                  |                     | $ab^{III}$       | 1    | 0    | 0         | 1                | 0                | 0                |

| III              | $u_b > u_c > u_a$   | $bc^{III}$       | 1    | 0    | 0         | 1                | 1                | 0                |

|                  |                     | $ca^{III}$       | 1    | 0    | 0         | 1                | 0                | 1                |

|                  |                     | $ab^{IV}$        | 1    | 0    | 0         | 1                | 0                | 1                |

| IV               | $u_c > u_b > u_a$   | $bc^{1V}$        | 1    | 0    | 1         | 0                | 0                | 1                |

|                  |                     | $ca^{IV}$        | 1    | 0    | 0         | 0                | 0                | 1                |

|                  |                     | $ab^{V}$         | 0    | 1    | 1         | 0                | 0                | 1                |

| V                | $u_c > u_a > u_b$   | $bc^{V}$         | 0    | 0    | 1         | 0                | 0                | 1                |

|                  |                     | $ca^{V}$         | 1    | 0    | 1         | 0                | 0                | 1                |

|                  |                     | ab <sup>VI</sup> | 0    | 1    | 1         | 0                | 0                | 0                |

| VI               | $u_a > u_c > u_b$   | $bc^{VI}$        | 0    | 1    | 1         | 0                | 0                | 1                |

|                  |                     | ca <sup>VI</sup> | 0    | 1    | 1         | 0                | 1                | 0                |

#### C. Improved Variable Step VBC

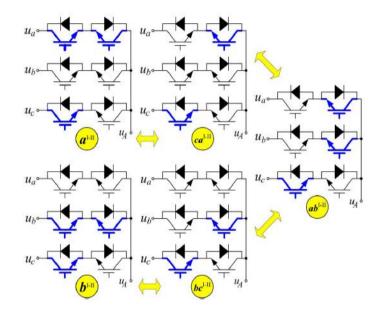

Based on Fig. 6 that the amplitude of input voltages is not clear, 6 critical intervals are placed between normal intervals. In each critical interval, two input voltages are similar to each other and measuring voltage amplitude related to each voltage is difficult. The commutation between two input phases that their voltages are clear is called uncritical commutation and the commutation between two phases that their voltages are not clear is called critical commutation. In each normal interval, all commutations are uncritical commutations and can be done in two stages but in critical intervals, the commutation method should be improved. When recognizing the amplitude of input voltages is difficult, to prevent short circuit, the main state must be determined. Consider critical interval I-II ( $U_a \cong U_b > U_c$ ), that the voltage amplitudes of  $U_a$  and  $U_b$  are not clear, if phase a is connected to the load, the unidirectional switches of phase b must not be turned on and vice versa. At first the main states are determined and then commutation states in each critical interval are presented in tables III and IV.

After determining switching states, uncritical commutation (in interval I-II, commutation between  $U_a$  and  $U_c$  and commutation between  $U_b$  and  $U_c$ ) can be performed base on VBC. Fig. 7 shows two-step uncritical commutation between  $U_a$  and  $U_c$  in critical interval I-II.

However, critical commutation (in interval I-II, between  $U_a$  and  $U_b$ ) can't be performed in two steps. Critical commutation can be achieved in two two-step commutations and causes doubling commutation time and witching losses.

Critical intervals are classified into two groups: H type and L type. In H type, two similar voltages are bigger that the third voltage and in L type, two similar voltages are lower than the third one.

In Fig. 8, the four-step critical commutation for commutating between  $\rm U_a$  and  $\rm U_b$  in interval I-II (H type) is shown.

Initial state  $a^{l-ll}$ : Both unidirectional switches in phase a are on, and both unidirectional switches in phase b are off, and the forward switch in phase c (S<sub>cAf</sub>) is on to create freewheeling path for positive current of the load.

Step 1) Commutation state  $ca^{1-11}$ : The forward switch of input phase a  $(S_{aAf})$  is turned off.

Step 2) Commutation state  $ab^{1-11}$ : The reverse switch of input phase b ( $S_{bAr}$ ) is turned off.

Step 3) Commutation State  $bc^{l\cdot ll}$ : The reverse switch of input phase a  $(S_{aAr})$  is turned off. Step 4) Target State  $b^{l\cdot ll}$ : The forward switch of input

Step 4) Target State  $b^{I-II}$ : The forward switch of input phase b ( $S_{bAf}$ ) is turned on. So, both switches of input phase b are on, both switches of input phase a are off, and the forward switch of phase c is still on to provide positive load current freewheeling path.

In the critical intervals type H, the forward switch of the third phase will be stayed on, and in type L, the reverse switch of the third phase will be stayed on.

Fig. 6. Normal intervals and critical intervals [1]

Fig. 7. Two-step uncritical commutation between  $U_a$  and  $U_c$  in critical interval I-II ( $U_a{>}U_c)\,[1]$

Fig. 8. Four-step critical commutation between  $U_a$  and  $U_b$  in critical interval I-II ( $U_a{\approx} U_b)$  [1]

TABLE III. MAIN SWITCHING STATES IN CRITICAL INTERVALS

| Critical intervals | Relative<br>voltage     | Main<br>state              | SaAf | SaAr | S <sub>bAf</sub> | S <sub>bAr</sub> | S <sub>cAf</sub> | S <sub>cAr</sub> |

|--------------------|-------------------------|----------------------------|------|------|------------------|------------------|------------------|------------------|

| intervais          | vonage                  | <i>a</i> <sup>I-II</sup>   | 1    | 1    | 0                | 0                | 1                | 0                |

| I-II (H)           | $u_a \approx u_b > u_c$ | <b>b</b> <sup>I-II</sup>   | 0    | 0    | 0<br>1           | 0<br>1           | 1                | 0<br>0           |

|                    |                         | $c^{\text{I-II}}$          | 0    | 1    | 0                | 1                | 1                | 1                |

|                    |                         | a <sup>11-111</sup>        | 1    | 1    | 0                | 1                | 0                | 0                |

| II-III (L)         | $u_b > u_a \approx u_c$ | <b>b</b> <sup>II-III</sup> | 1    | 0    | 1                | 1                | 1                | 0                |

|                    |                         | $c^{\text{II-III}}$        | 0    | 0    | 0                | 1                | 1                | 1                |

|                    |                         | <i>a</i> <sup>111-1V</sup> | 1    | 1    | 0                | 1                | 0                | 1                |

| III-IV (H)         | $u_b \approx u_c > u_a$ | $b^{\text{III-IV}}$        | 1    | 0    | 1                | 1                | 0                | 0                |

|                    |                         | $c^{\text{III-IV}}$        | 1    | 0    | 0                | 0                | 1                | 1                |

|                    |                         | a <sup>IV-V</sup>          | 1    | 1    | 0                | 0                | 0                | 1                |

| IV-V (L)           | $u_c > u_b \approx u_a$ | <b>b</b> <sup>IV-V</sup>   | 0    | 0    | 1                | 1                | 0                | 1                |

|                    |                         | c <sup>IV-V</sup>          | 1    | 0    | 1                | 0                | 1                | 1                |

|                    |                         | a <sup>V-VI</sup>          | 1    | 1    | 1                | 0                | 0                | 0                |

| V-VI(H)            | $u_c \approx u_a > u_b$ | <b>b</b> <sup>V-V1</sup>   | 0    | 1    | 1                | 1                | 0                | 1                |

|                    |                         | $c^{V-VI}$                 | 0    | 0    | 1                | 0                | 1                | 1                |

|                    |                         | a <sup>VI-I</sup>          | 1    | 1    | 1                | 0                | 1                | 0                |

| VI-I (L)           | $u_a > u_c \approx u_b$ | <b>b</b> <sup>VI-I</sup>   | 0    | 1    | 1                | 1                | 0                | 0                |

|                    |                         | $c^{VI-I}$                 | 0    | 1    | 0                | 0                | 1                | 1                |

TABLE IV. COMMUTATION SWITCHING STATES IN CRITICAL INTERVALS

| Critical intervals | Relative<br>voltage           | Main<br>state        | SaAf | SaAr | S <sub>bAf</sub> | S <sub>bAr</sub> | $S_{cAf}$ | S <sub>cAr</sub> |

|--------------------|-------------------------------|----------------------|------|------|------------------|------------------|-----------|------------------|

|                    | $u_{a} \approx u_{b} > u_{c}$ | ab <sup>I-II</sup>   | 0    | 1    | 0                | 1                | 1         | 0                |

| I-II (H)           |                               | $bc^{I-II}$          | 0    | 0    | 0                | 1                | 1         | 0                |

|                    |                               | $ca^{I-II}$          | 0    | 1    | 0                | 0                | 1         | 0                |

|                    |                               | ab <sup>II-III</sup> | 1    | 0    | 0                | 1                | 0         | 0                |

| II-III (L)         | $u_b > u_a \approx u_c$       | $bc^{\text{II-III}}$ | 0    | 0    | 0                | 1                | 1         | 0                |

|                    |                               | ca <sup>II-III</sup> | 1    | 0    | 0                | 1                | 1         | 0                |

|                    |                               | ab <sup>III-IV</sup> | 1    | 0    | 0                | 1                | 0         | 0                |

| III-IV (H)         | $u_b \approx u_c > u_a$       | bc <sup>III-IV</sup> | 1    | 0    | 0                | 1                | 0         | 1                |

|                    |                               | ca <sup>III-IV</sup> | 1    | 0    | 0                | 0                | 0         | 1                |

|                    | $u_c > u_b \approx u_a$       | ab <sup>IV-V</sup>   | 1    | 0    | 1                | 0                | 0         | 1                |

| IV-V (L)           |                               | bc <sup>IV-V</sup>   | 0    | 0    | 1                | 0                | 0         | 1                |

|                    |                               | ca <sup>IV-V</sup>   | 1    | 0    | 0                | 0                | 0         | 1                |

|                    |                               | ab <sup>V-VI</sup>   | 0    | 1    | 1                | 0                | 0         | 0                |

| V-VI (H)           | $u_c \approx u_a > u_b$       | bc <sup>V-VI</sup>   | 0    | 0    | 1                | 0                | 0         | 1                |

|                    |                               | ca <sup>V-VI</sup>   | 0    | 1    | 1                | 0                | 0         | 1                |

|                    |                               | ab <sup>VI-I</sup>   | 0    | 1    | 1                | 0                | 0         | 0                |

| VI-I (L)           | $u_a > u_c \approx u_b$       | bc <sup>VI-I</sup>   | 0    | 1    | 1                | 0                | 1         | 0                |

|                    |                               | ca <sup>VI-I</sup>   | 0    | 1    | 0                | 0                | 1         | 0                |

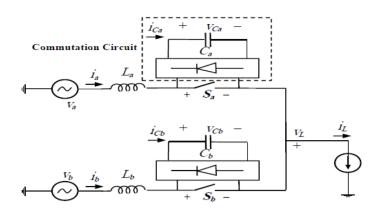

# IV. A ROBUST COMMUTATION CIRCUIT FOR RELIABLE SINGLE STEP COMMUTATION

In multi – step commutation methods that based on current sign or input voltage magnitude, when the output current or the input voltage are small, the commutation task can be gotten error. Decreasing commutation time causes to increase input and output waveforms quality. Commutation time can be decreased by decreasing the number of steps from four to two or one while the commutation algorithm will be been more complicated. In aerospace applications that the range of frequency is 360 – 800 Hz, decreasing commutation time is one of the main goals. In this part, a new single-step commutation circuit for matrix converter is considered that provides a reliable bidirectional path for the load current during the commutation and protects the keys from the overvoltage. This commutation circuit is connected across each switch directly and does not need clamp circuit. The main advantage of this commutation circuit is that has a fairly short delay time ( about nanoseconds). This single-step delay reduces the commutation time significantly in compared with multi-step methods. This method doesn't require current and/or voltage measurement.

The main elements of commutation circuit include: 1) diode bridge 2) capacitor 3) energy mitigation circuit  $(EMC^1)$ , the operation of EMC is that to waste the stored energy in the capacitor through a resistive component or to return the stored energy back to the system.

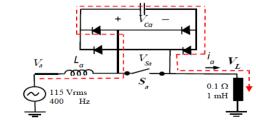

Fig. 9 shows a matrix converter circuit with commutation circuit that placed across each switch. The commutation circuit provides a bidirectional path for load current using a delay time during commutation. The analysis considers the inductive feature of the circuit. The commutation process includes:

- 1) Opening the outgoing switch.

- 2) Transferring the load current to the commutation circuit.

- 3) Closing the incoming switch after the turn on delay.

Fig. 9. Matrix converter with commutation circuit [4]

## A. Pre – commutation ( $S_a$ closed, $S_b$ open)

At first, the switch of phase a  $(S_a)$  is closed and the load is supplied by  $V_a$ ,  $i_a=i_L$ ,  $i_b=0$ , and the load voltage and the voltage across the switch Sb are:

$$V_L = V_a - L_a \frac{dia}{dt} \tag{1}$$

$$V_{sb} = V_b - V_L,$$

$$= V_b - V_a + L_a \frac{dia}{dt}$$

(2)

Equation (2) is valid when the diode bridge is blocked in phase b and  $V_{cb}>V_{ba}$ , assuming the load current during the short period is constant, i.e.,  $\frac{dia}{dt}=0$ . Otherwise, the bridge conducts and the voltage across  $S_b$  is  $V_{cb}$ . To satisfy this condition, the commutation capacitor voltage should be more than line-line voltage.

$$V_{ci} > |V_{ab}|, \qquad i=a,b \qquad (3)$$

# B. During-Commutation ( $S_a$ open, $S_b$ open and then closed)

In this conditions, commutation process cab be considered in two stages: 1) the load current transfer from  $S_a$  to the commutation circuit of phase a (turn-on delay), and 2) the load current transfer from commutation circuit of phase a to switch  $S_b$  after closing  $S_b$  (transition delay).

1- Turn-on delay ( $S_a$  open,  $S_b$  open)

Switch  $S_a$  is turned off and  $S_b$  is Turned on. Since the turnon delay strategy is adopted for the safe operation of the switches,  $S_b$  is turned on after time delay  $t_d$ . Upon  $S_a$  turn-off instant, the load current flows through the commutation circuit,  $i_L=i_a=i_{ca}$  and  $V_a$  supplies the load still. The load current flows in commutation capacitor and charges the capacitor:

<sup>&</sup>lt;sup>1</sup> Energy Mitigation Circuit

$$V_{ca} = V_{ca0} + \frac{1}{c} \int_{td} i_a dt$$

(4)

Where  $V_{ca0}$  is the capacitor initial voltage. Since the diode bridge across the  $S_a$  is open and conducts the load current, the capacitor voltage appears across the  $S_a$ .

$$V_{sa} = \pm V_{ca} \tag{5}$$

Positive or negative sign in equation (5) is depended on the current sign. In the following, the current sign is assumed positive. The voltage across the load and  $S_b$  are:

$$V_L = V_a - L_a \frac{dia}{dt} - V_{ca} \tag{6}$$

$$V_{sb} = V_b - V_a + V_{ca} + L_a \frac{dia}{dt}$$

(7)

2- Transition delay, transition from commutation circuit in phase a to switch S<sub>b</sub> (S<sub>a</sub> open, S<sub>b</sub> closed)

After time  $t_d$ ,  $S_b$  is closed. Because of  $L_a$  and  $L_b$ , the current can't be instantaneously transferred from phase a to phase b. The capacitor in the bridge of phase a conducts until its current becomes zero. This transition interval depends on the inductances  $L_a$  and  $L_b$ . In this condition, both  $V_a$  and  $V_b$  participate in current load and we have:

$$V_L = \frac{1}{2} \left( V_a + V_b - L_a \frac{dia}{dt} - L_b \frac{dib}{dt} - V_{ca} \right) \quad (8)$$

When the bridge in phase a conducts, the voltage across the switch  $S_a$  is  $V_{ca}$ . For symmetrical system where  $L_a=L_b$ , the rate of change of currents  $i_a$  and  $i_b$  are the same, but the current directions are different and thus the differential terms in (8) cancels out.

#### C. Post-Commutation ( $S_a$ open, $S_b$ closed)

During the post-commutation, the load current flows phase b totally and the diode bridge in phase b is turned off by  $V_{ca}$ . The conditions in this state are: 1)  $V_{sb}=0, 2$   $i_b=i_L, 3$   $i_a=0$ .

The load voltage and the voltage across the switch S<sub>a</sub> are:

$$V_L = V_b - L_b \frac{dib}{dt} \tag{9}$$

$$V_{sa} = V_a - V_b + L_b \frac{dib}{dt} \tag{10}$$

This point should be mentioned that the real delay in the above system is just td and the gate signals after  $t_d$  can be updated after td that are in range of hundred nanoseconds.

# D. Commutation circuit performance

The main feature of commutation circuit is to create an auxiliary path for the load current during commutation when all switches are open. During this time, the load current charges the commutation capacitor and the switch voltage is capacitor voltage. Because the same gate signals are applied to both switches in one bidirectional AC switch, the number of gate drivers can be reduced to half as compared to the other multi-step methods. The performance of the commutation circuit is depended on  $t_d$ . During these periods, the line current charges the commutation capacitor. The capacitor voltage is based on (4). If there is no auxiliary path for discharging the capacitor, the capacitor voltage is increased based on (5) and (7).

An energy mitigation circuit can be used to regulate the capacitor voltage. The EMC average power rate is lower than 3% of the total average power rate of the unit that determined based on switches type, duration of delay time, and switches turn-on/off delay compensation for PWM pattern. The stored energy in the capacitor based on some issues such as  $t_d$ , unit rate, and price can be mitigated by resistive elements or turned to the system back. For low power applications, this energy is mitigated by resistive elements, but this energy turned back to the system by a circuit in huge applications.

The switch voltage was explained by (2), (5), (7), and (10) Equation (7) prepared the maximum voltage of the key  $V_{ba}+V_{ca}$  (line voltage plus commutation capacitor voltage) when the sign isn't negative. However, equation (3) shows the diode bridge is open and the voltage of S<sub>b</sub> is equal to V<sub>cb</sub> and isn't V<sub>ab</sub>+V<sub>ca</sub>. This is used as the switch overvoltage protection index. So, by maintaining the capacitor voltage level higher than natural commutation voltage, the maximum voltage of the switch can be obtained. Fig. 10 shows a deeper insight of overvoltage issue in matrix converter. As the worst condition, an inductive load is assumed. When S<sub>a</sub> is closed;

$$VL = Va - La \frac{dia}{dt}$$

(11)

And when S<sub>a</sub> is open:

$$VL = Va - Vca - La \frac{dia}{dt}$$

(12)

In (11), the dominate voltage across the load is  $V_a$  while in (12), the dominate voltage is  $(V_a - V_{ca})$ . When  $V_{ca}$  is greater than  $V_a$ , the load voltage is negative and the current goes to zero.

Fig. 10. Study system for the overvoltage analysis [4]

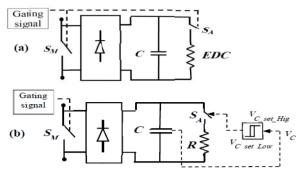

Based on different types of EMCs and control methods, the following enhanced configurations of the proposed commutation circuit can be realized.

# A. Type-1 commutation circuit

This configuration is shown in Fig. 11 that switch  $S_M$  is the main switch and switch  $S_A$  is the auxiliary switch of the energy dissipative circuit  $(EDC^2)$ . Type-1 configuration is simple and both the main and auxiliary switches are locked, the same gate signal is applied to both switches. The main feature of this configuration is that has fully discharging capable for capacitor before doing the next commutation process. During turn-on period, S<sub>A</sub> is closed and C is fully discharged through R. When the turn-off signal is applied to both  $S_M$  and  $S_A$ switches (for example in phase a in Fig. 9), the load current in the main switch is transformed to commutation circuit of phase a. When the capacitor is fully discharged, it provides nearly zero switching voltage during turn-off period. The capacitor size should be reduced to a level that the load current can charge the capacitor up to the line voltage during the commutation period.

$$C = \frac{iL\Delta t}{\Delta v} \tag{11}$$

Where  $\Delta t = t_d$  and  $\Delta v = V_{ab}$ . The advantage of this structure is that the commutation capacitor is discharged through the EDC during the turn-on period and provide zero voltage and zero current conditions for the main and auxiliary switches during turn-off period, respectively.

#### B. Type 2a commutation circuit

The commutation circuit type 2a is shown in Fig. 11-b. In this configuration, the commutation capacitor is charged to more than the natural commutation voltage (V<sub>c-set-low</sub>). However, the diode bridge is blocked by the capacitor voltage while the main switch is off and no current flows in bridge in off or on state at normal instant operation, however during the commutation, since there is no path for load current, except commutation capacitor, the load current opens the diode bridge and flows through commutation capacitor. In commutation instant, the capacitor is charged to the voltage given in (4).  $V_{c0}$  is equal to  $V_{c-set-low}$ . The stored energy during the commutation can be returned to the system back by an Energy recovery circuit (ERC $^3$ ) or dissipated is resistive elements. For simplicity, ERC is presented by S<sub>A</sub> and R in Fig. 3. For regenerating the stored energy during the commutation and preventing the overvoltage, the below control strategy is applied to auxiliary switch:

Volume 13, 2019

Fig. 11. a) commutation circuit type-1, b) commutation circuit type 2a [4]

- 1) Observe the capacitor voltage ( $V_c$ ) and compare with the upper present value of  $V_{c-set-high}$ .

- 2) When V<sub>c</sub> is greater than V<sub>c-set-high</sub>, the turn-on signal is applied to auxiliary switch and the capacitor energy is transferred to ERC.

- 3) When V<sub>c</sub> is equal or lower than V<sub>c-set-low</sub>, the turn-off signal is applied to auxiliary switch to stop the capacitor discharging and keep the capacitor voltage greater than the natural commutation voltage.

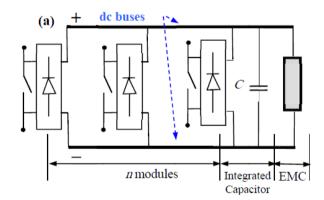

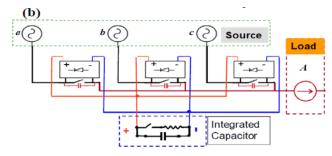

# C. Type 2b commutation circuit (integrated capacitor)

The commutation circuits type-1 and 2a are designed for each AC switch. This fact that the commutation capacitor voltage in type 2a is charged to more than commutation voltage suggests the integration of all capacitors as one capacitor. Fig. 12 shows the commutation circuit type 2b for a matrix converter with n main AC switches. The basic circuit of a three-phase-to-one-phase matrix converter included  $IC^4$  is shown in Fig. 13. The main feature of this structure is that the load current can be diverted to one capacitor and the hysteresis control for EMC can be used.

Fig. 12. Type 2.b commutation circuit [4]

<sup>&</sup>lt;sup>2</sup> Energy Dissipative Circuit

<sup>&</sup>lt;sup>3</sup> Energy Recovery Circuit

<sup>&</sup>lt;sup>4</sup> Integrated Capacitor

Fig. 13. A three-phase-to-one-phase ICMC [3]

## VI. USING RBIGBT TO SOLVE THE COMMUTATION PROBLEM

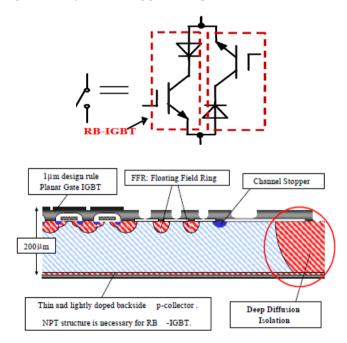

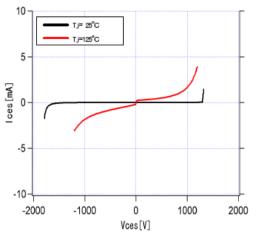

The RBIGBT has a symmetrical blocking voltage characteristic. This means that it can block both forward and reverse voltage in its off state. So, the structure of bidirectional switch is simplified because the diodes are eliminated. Many commutation problems can be solved by this switch. This switch is used in small applications, but not produced yet for industrial and big applications. In this part, a 1200 v and 100 A RBIGBT is considered. The basic structure of RBIGBT is shown in Fig. 14. The RBIGBT is similar to conventional IGBT with this difference that it has a deep diffusion collector wall surrounding the cheap active area. This isolation by collector allows the RBIGBT to block the reverse voltage. This isolation is designed by a special process to keep a high breakdown voltage and stable leakage current at elevated temperatures by minimizing processing time.

Fig. 14. RBIGBT structure [3]

# A. RBIGBT features

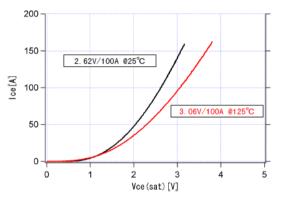

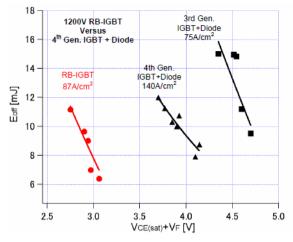

The RBIGBT has the symmetrical voltage blocking that shown in Fig. 15. It has low and stable leakage current at elevated temperatures in both directions. Fig. 16 shows the onstate of RBIGBT voltage based on the collector current. The on-state voltage is up to 3 v that 0.75 is lower than the fourth generation IGBT with series diode. This means that the conductance losses have been reduced. Table V compares a RBIGBT with an IGBT with series diode.

Fig. 15. RBIGBT symetrical voltage blocking [3]

Fig. 16. RBIGBT voltage vs collector current [3]

TABLE V. COMPARING THE LOSSES

| Item       | RB-IGBT | 4 <sup>th</sup> IGBT + Diode |

|------------|---------|------------------------------|

| Von (v)    | 3.06    | 3.8                          |

| Esw (mJ/p) | 11.6    | 19.1                         |

| Err (mJ/p) | 11.7    | 12.2                         |

Fig. 17. Energy of switches vs voltage [3]

Fig. 17 also compares the switch energy with the RBIGBT on-state voltage, the third generation IGBT, and the fourth generation IGBT. From Fig. 17 can be understood that the RBIGBT reduces the losses and is more suitable for matrix converter applications.

# VII. SIMULATION

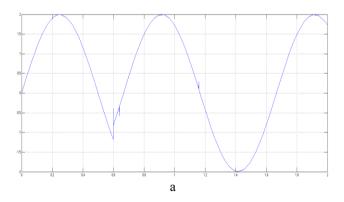

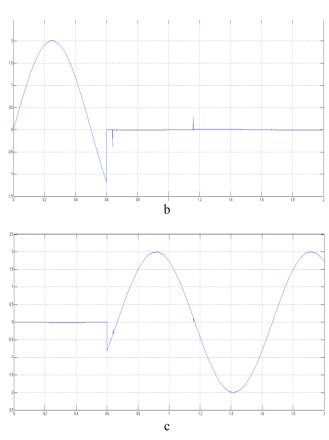

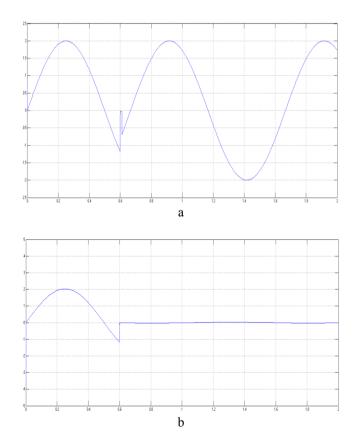

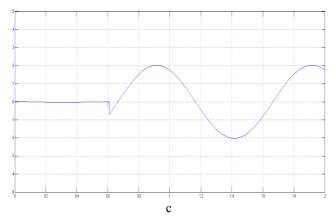

By simulation using MATLAB, the commutation circuits will be considered. The simulation has been done for commutation circuit based on current sign detection and commutation circuit type-1 using hysteresis control. Fig. 18 shows the simulation results of commutation circuit based on current sign detection. Fig. 19 shows the results of commutation circuit type-1.

As it is obvious from Fig. 18, at the time t=0.6 sec, the commutation from phase a to phase b has been done. In this time, the load current was negative and an increasing in load current has been occurred during the commutation.

It is concluded from Fig. 19 that the occurred overcurrent in the previous circuit has been solved and the commutation time has been decreased.

Fig. 18. Commutation based on current sign detection, a) load current, b) phase A current, c) phase B current

Fig. 19. Commutation circuit type-1 with hystersis control, a) load current, b) phase A current, c) phase B current

#### VIII. CONCLUSION

In this seminar, some of the commutation methods in matrix converter including commutation based on current sign detection, voltage based commutation, and the commutation by single-step commutation circuit have been introduced and considered. The commutation implementation based on current sign detection can be gotten error in nearly zero current instants and also in this method, the commutation is performed in four stages that causes more disturbances in waveforms itself. The voltage base commutation (VBC) doesn't need to measure the current and obtain its sign, from this sight of view, there isn't the probability of error and the commutation is done in two steps except the critical intervals that done in four steps and it reduces the commutation time, but from this aspect that done in two and four steps, it can create the disturbances in the waveforms. Finally, the commutation performance by the single-step commutation circuit decreases the commutation time really and create less disturbances in the waveforms that can be a good option for matrix converter. But the best option for matrix converter seems using RBIGBT that isn't challenged by commutation problems and has lower losses, but it has not produced in the industry widely.

# REFERENCES

- S. Hongwu, L. Hua, H. Bi, W. Wingwei, Y. Limin, and A. Xing, "Implementation of voltage based commutation in space vector modulated matrix converter," IEEE Transaction on industrial electronics, vol. 59, pp. 154-166, 2012.

- [2] C. Klumpner and F. Blaabjerg, "Fundamentals of the matrix converter technology," Aalborg University, pp. 61-75, 2002.

- [3] E.R. Motdo, J.F. Donlon, M. Tabta, H. Takahashi, Y. Yu, and G. Majumdar, "Application characteristics of an experimental RBIGBT (reserve blocking IGBT) module," Powerex incorporated USA, pp. 1-5, 2004.

- [4] S.A. Nabavi Niaki, R. Iravani, and H. Kojori, "A robust commutation circuit for reliable single step commutation of the matrix converter," IEEE Papers, pp. 3349-3355, 2014.