# High-phase Resolution Architecture for Phased Array Transmitters

F. Cannone, G. Avitabile, G. Coviello

Abstract— The paper describes a frequency independent phase shifting technique suitable for applications wherein a high-phase resolution at RF frequencies is required. For instance the propose approach is useful both for advanced measurements systems and for RADAR, satellite and wireless telecommunications systems. The proposed phased array transmitter is based on an innovative technique using the cascade of two blocks: an advanced digital block named Phase Control Block and an up-converter block containing integer-PLLs. The first digital block assures a high phase resolution comparable with the precision achievable by using a Direct Digital Synthesizer. The second block allows the up conversion at microwaves frequencies without a significant decrease of the phaseshift precisions. In fact, thanks to the described technique, the phase resolution is limited only by the rms phase error introduced by the integer-PLLs. The theory governing the design of the phase shifter is thoroughly discussed and three prototypes operating in different bands reporting an rms phase error lower than 0.4 degrees are reported. The measurements are compared with theoretical results showing a perfect agreement.

*Keywords*— Phase shifter, Microwave circuits, Antennae array, Phase Locked Loop (PLL).

#### I. INTRODUCTION

LECTRONIC phase shifters are employed in several Eways in advanced measurements systems, RADAR, satellite and wireless communication applications [1]-[4], mostly for antennae array design. The main advantages of commonly used structures are high directivity, interference rejection, fast scanning rate and signal to noise ratio improvement. The higher is the number of elements combined in the array the more evident are the advantages of phased arrays. Moreover, the modern radar and communications transceivers have to provide multi-mode and multi-band operations. In phased array systems this means for instance, to have the possibility to track multiple targets in electronic radar countermeasure and systems or multi-point communications. All these requirements place an increasing interest in phase shifters.

The recent literature presents various techniques for phase shifter structure [5]. The use of transmission lines or metamaterial transmission lines with distributed loads gives rise to distributed-type phase shifters (DTPSs) which have as an alternative the approach based on a vector sum of two or more orthogonal-phased signals and the phase shifters based on an all-pass network [5]-[11].

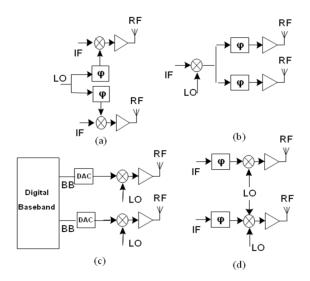

A second classification can be made depending on the position of the phase shifters in the Tx/Rx module: LO, IF, RF or base band phase-shifting architecture are possible [4]. Several solutions have been proposed, each one suitable for a specific application. Recently both for RADAR, satellite and wireless communication applications, the demand of programmable and reconfigurable Tx/Rx modules has been increasingly pushed by the advances in the field of software radio architectures. This calls for novel topologies and solutions.

In [12] it is described a programmable phase shifter based on a Direct Digital Synthesizer (DDS). In this approach the RF digital phase shifter in the transmitter path has been substituted by the phase shift function of a DDS followed by a mixer for the up conversion. The LO-path phase shifting technique is an alternative approach that has produced interesting phased array systems [13[-[15]. These reported LO phased array transmitters are based on the heterodyne architecture.

In the case of modulation schemes based on the PSK or FSK, an alternative architecture is that based on the PLLs used in the transmitter path. The Sigma-Delta fractional-PLLs are the classical implementation that allows to achieve good performances and high data rates limited mostly by the band of the PLL. Moreover, different solutions to overcome this band limit are possible [16]-[18].

In [19]-[22] are presented some techniques to use a PLL in the phase shifter architecture.

The architecture described in this paper, is based on the phased array transmitter described in [23]-[25] and investigates the possibility to use the LO phase shifting technique along with the PLL based transmitter. This novel topology has been introduced as an alternative to very high phase resolution architectures, such as those based on the DDS, with the additional feature of frequency scalability.

The main achievement is a very high phase resolution available for different ranges of frequencies. Indeed the rms phase error is limited only by the rms phase error of the PLLs. It is also important to highlight two other features. First, the number of bit is easily scalable since a higher phase resolution is achieved simply by modifying the digital part of the

F. Cannone is with the Politecnico di Bari, D.E.I., Bari, BA 70125 Italy (phone/fax: +39-080-596-3854; e-mail: f.cannone@poliba.it).

G. Avitabile is with the Politecnico di Bari, D.E.I., Bari, BA 70125 Italy (e-mail: gfa@poliba.it).

G. Coviello is with the Politecnico di Bari, D.E.I., Bari, BA 70125 Italy (e-mail: g.coviello@poliba.it).

architecture. Second, the phase steps are controlled by the digital block and therefore the architecture is capable to be used for every digital beam-forming and calibration technique. In general, a lot of error sources exist in the front end which motivate the adoption of a calibration technique. For instance, [26] demonstrates that the calibration is a good solution to reduce the phase deviation due to the changes in the power supply and the deviation across different prototypes due to process variations.

The paper reports the measurements of three prototypes operating in three different bands showing a similar rms phase and errors lower than 0.4 degrees. The paper is organized as follows: section II briefly introduces and discusses qualitatively the proposed transmitter; section III describes in details its operations. Finally, the three prototypes are described and experimentally validated in section IV.

#### II. PHASE SHIFTER ARCHITECTURE

## A. Current architecture overview

An ideal phased array transmitter consists of several signal paths each one connected to different antennas. The beam forming is achieved by varying the relative time delay between the signals feeding each single element of the antenna. The beam forming does not depend from the frequency and the bandwidth of the signal when governed by true time delays. In practical phased arrays, it is difficult to design tunable, broadband delay blocks but it is possible to approximate the uniform delay with a constant phase shift over a moderate signal bandwidth. This approximation, even maintaining the wanted coherence for the carriers, introduces a distortion of the baseband modulation signals that depends on the signal bandwidth. The higher is the ratio between the bandwidth and the carrier, the higher is the baseband time incoherence, which means a degradation of the error vector magnitude (EVM), which is also a function of the incidence angle at the receiver. In narrow band applications, the constant phase shift approximation is a viable solution. Moreover, unlike the wideband case, the phase shift technique in the case of narrowband signals can be implemented at RF, LO, IF, baseband level or, even, in digital domain. Each of the previous possibilities corresponds to a different phase shifter architecture. In Fig.1 these classical architecture of phased array transmitter are reported.

As stated before, in narrow band applications the constant phase shift approximation is a viable solution at RF, LO, IF, baseband or digital domain level [13]. The RF phase shifting technique is considered the most cost-effective solutions mostly for systems requiring a big number of elements [4].

A low-loss RF phase shifter is a challenging building block at high frequencies, and it is difficult in practical implementations to achieve low losses joint to uniform performances for the different phase shifts. In spite of these difficulties, good results in terms of phase variations have been reported for medium phase resolution systems.

For instance, in [27] a phase variation less than 8.8 degrees

for all the 4-bit phase states at 35-50 GHz is shown.

Fig. 1 Phase shifting architectures: (a) LO path phase shifting ; (b) RF phase shifting; (c) base band phase shifting; (d) IF phase shifting.

The LO-path phase shifting technique requires more components than an all-RF architecture but introduces several advantages relaxing, for instance, the impact of the insertion losses variations on the system's performances. Phased array systems adopting this approach and achieving interesting results are described in [13]-[15].

Digital array architectures are very flexible but in general lead to expensive and not power-efficient solutions for a given phase resolution and band of frequencies. The higher is the frequency the less the DDS is feasible in terms of power consumption.

The proposed architecture, is different in that it gives the possibility to use the LO phase shifting idea along with the PLL based architecture in order to obtain higher phase resolution.

## B. The proposed architecture basics

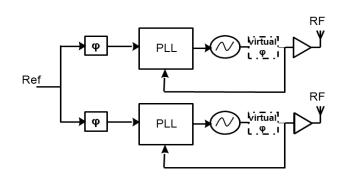

The core of the proposed transmitter is a PLL configuration that is able to perform simultaneously the LO phase shifting and the up conversion. The LO phase shifting is achieved by controlling the signal used as references for the PLLs. Two basic blocks for the proposed approach are depicted in Fig. 2.

Fig. 2 Proposed phase shifting architecture.

The phase shifting is introduced on the signal used as references for the PLLs and, thanks to the techniques explained in the next sections, it implements a virtual LO phase shifting. Since the phase shifting is implemented at high frequencies but is controlled at low frequencies, it is easier to achieve the desired high phase resolution for a given band of frequencies if compared with traditional approaches.

Among the reported phased array transmitters based on a PLL, in [22] an interesting architecture that uses a variablephase ring oscillator (VPRO) was presented. This solution reduces the area and power requirements by eliminating a number of key building blocks. The architecture does not aim to a high phase resolution and a 3-bit operation is reported. Even though the principles underneath such transmitter are quite different, also the proposed approach allows to eliminate a number of key building blocks. Nevertheless, the proposed solution reaches its outstanding high phase shift resolution at the expense of more components than the architecture in [22], therefore it is more suitable in those applications where the key issue is the phase resolution while the complexity and power consumption are less crucial.

The proposed approach seems to be to the authors one of the best reported solution for improving the phase shift resolution; looking at the complexity, integration and power consumption, this architecture is comparable to those adopting the LO-path phase shifting. This means that it is not the most cost-effective solution if compared to the all-RF architectures.

In particular, for what concerns the integration, it is possible to make some considerations from a system level point of view. Assuming to use a silicon RFIC process, the proposed architecture is suitable for integrating on the same chip a smaller number of modules than an all-RF phase shifter architecture like the architecture based on IF, LO or Base Band. Since the all-RF approach allows to simplify the control routing in a large array is therefore the more suitable solution from a scalability point of view.

Similar considerations can be made for the power consumption. The main drawbacks in this case derives from the presence of a VCO and a divider in each branch, which are the more power consuming components. The proposed architecture can provide the same phase resolution of a DDS phase shifter with the important advantage of moving in the RF domain such capability. In those applications where a very high phase resolution is necessary, for instance a single phase shifter for instrumentation at high frequencies, the proposed architecture can be considered a low-power solution when compared to the high-frequency DDS mandatory needed due to the fact that the up converter mixer otherwise would deteriorate the DDS phase shift resolution.

The proposed approach if compared with the classical LOpath phase shifting based on the heterodyne architecture evidences analogies and differences. The losses and the amplitude mismatches introduced by phase shifters controlling the reference signals do not affect the phased array transmitter performances, similarly to the case of phased array in [13]- [15], since the digital phase and frequency detector (PFD) works independently from the amplitude level of its inputs, following theirs rising (falling) edges. In heterodyne architectures, the LO signals are in RF domain. This means that the phase shifters used to achieve the LO-path phase shifting, even if, have relaxed constraints, are designed to operates at RF. Although good design approaches are possible to achieve high-resolution RF phase shifters [15], it still remains a challenging task. The proposed topology does not rely on these blocks. Indeed, exploiting the lock mechanism of the PLLs, the LO phase shifting is achieved directly managing the reference signals. Moreover, since the up conversion is performed contextually at the phase shifting of the LO, any mismatch introduced by the up converter is cancelled by the closed loop operation. Finally, one of the main challenge which limits the phase resolution achievable by a classical LOpath phase shifter is the design of the LO distribution network [4],[26]. The proposed approach strongly relaxes this problem because the LOs are present in each module and the signals that need to be routed are in the baseband or IF domain.

#### C. Open questions: the bandwidth and the receiver structure

The main open questions among the others that need attention are the channel bandwidth and a proposal on the receiver side. This paragraph reports some qualitative considerations.

A limit to the channel bandwidth is imposed by the cut off frequency of the PLL loop filter. This problem could be overcome by using techniques like the on-channel and twopoint modulation. As an alternative, in applications which require wider bandwidths, it is possible to use the proposed phase shifter not as the complete phased array transmitter, but as the sub-block which implements the local LO-path phase shifting [28] at the expense of adding a mixer in each branch. Indeed, in this assumption the channel bandwidth is still not linked to the one of the PLL.

This latter solution is at the same time the more direct way to use the proposed transmitter into the receiver path. In this case the analysis of the expected performances of the receiver module is similar to that described in the papers reporting those architectures.

## **III. PHASE SHIFTER OPERATIONS**

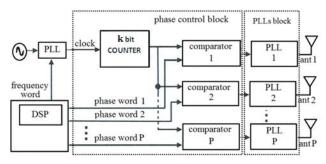

The simplified block diagram of the proposed architecture, is depicted in Fig.3. This advanced Phase Control Block(PCB)-PLLs phase shifter has two main blocks: the PCB and the PLLs block. The PCB is a digital block which provides the phase-shifted squared waves with a phase-shift precision equal to  $360^{\circ}/2^{k}$  being k the number of bits of the PCB. The number of squared waves, P, corresponds to the number of paths or channels to the antennas. The inputs to the PCB are the PLL reference clock and the P input phase words. These latter can be provided to the PCB by using a DSP or a microcontroller; these words set for each path to the antennas the desired phase shifts. The second block contains P integer-PLLs which up-convert to the microwaves frequencies the phase-shifted squared waves provided by the PCB. The process of up conversion occurs without a significant decrease of the phase-shift precisions.

Fig. 3 Phase Control Block-PLLs Phase Shifter Architecture.

The proposed solution has the evident advantage that allows to reach the wanted phase resolution (for instance, the resolution wanted for implementing a calibration technique) without impacting the complexity of the overall architecture. The basic idea is to use the Phase Control Block to reach the high phase resolution and the PLLs to up convert the signals without compromising the signal integrity and phase resolution. It is possible in the digital world to design a low power and high performances PCB with a big number of bits for the wanted very high phase resolution (to a feasible 14-bit PCB correspond a phase steps equal to about  $0.02^{\circ}$ ). Nevertheless, it is not possible to use directly such a digital block with an up converter. In fact, the multiplication using PLLs compromises the signal integrity and the phase resolution, while the up-conversion using a mixer may in addition require difficult or impossible output filtering.

#### A. PCB-PLLs phase shifting techniques

A first way to deal with the degradation of phase resolution using a PLL as up-converter, is to use an offset-PLL, i.e. a PLL with a mixer in the feedback path instead of the divider. As demonstrate in [23], the mixer in the feedback path of the offset-PLLs shifts the RF VCO output to an IF frequency, so that no phase degradation occurs. This approach provides the capability to take advantage of the digital block at microwave frequencies. A key point of this topology is the design of the local oscillator that drives the mixers. Indeed, when this architecture is used to generate high frequency signals, the LO is a microwave oscillator. Taking into account that the transfer function between the LO input of the mixer and the PLL output has a low-pass nature, it is necessary to design a low phase noise VCO in order to not increase the rms phase error of the PLL.

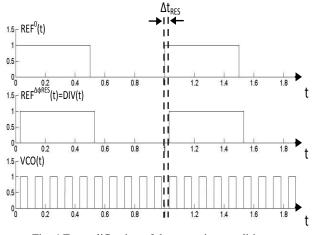

A second way has been presented in [24],[25]. Under rigorous condition, it is possible to use a divider into the feedback path of the PLL, as alternative or joint to the mixer, without deteriorating the phase resolution. In fact, for using a M divider in the feedback loop is sufficient to link the choice of M to the reference frequency, to the wanted output frequency and the number of bit, k, of the accumulator. In Fig. 4 the operating condition is exemplified. Let  $\text{REF}^{0}(t)$  be the reference signal for the other shifted signals provided by the phase control block,  $\text{REF}^{\Delta\phi\text{RES}}(t)$  the reference signal for the PLL which has a minimum phase shift equal to  $\Delta\phi_{\text{RES-IN}}$  with respect to  $\text{REF}^{0}(t)$  and VCO(t) the squared output of this PLL. When the PLL, which has as input  $\text{REF}^{\Delta\phi\text{RES}}(t)$ , is locked, then its squared output VCO(t), has the rising edges aligned with the rising edge of its input, while the squared output of the PLL used as reference has the rising edges aligned with the rising edges of  $\text{REF}^{0}(t)$ .

Fig. 4 Exemplification of the operating condition.

In such an operating condition, the two inputs and the two outputs of the two considered PLLs are delayed of the same amount of time, equal to  $\Delta t_{RES}$ . In particular, being  $\Delta \phi_{RES-IN}$  the minimum achievable phase shift, then  $\Delta t_{RES}$  represents the minimum time delay between the signals that drive the PLLs. The relation between  $\Delta \phi_{RES-IN}$  and  $\Delta t_{RES}$  is expressed in (1)

$$\Delta t_{\rm RES} \rightarrow \Delta \phi_{\rm RES-IN} = \frac{\Delta t_{\rm RES}}{T_{\rm IN}} \cdot 2\pi$$

(1)

where  $T_{IN}$  is the reference period at the input of the PLL. At the output of the PLL occurs the same time delay,  $\Delta t_{RES}$ , to which corresponds a phase shift,  $\Delta \phi_{RES-OUT}$ , equal to  $M \cdot \Delta \phi_{RES-IN}$

$$\Delta t_{\text{RES}} \rightarrow \Delta \phi_{\text{RES}-\text{OUT}} = \frac{\Delta t_{\text{RES}}}{T_{\text{OUT}}} \cdot 2\pi = M \cdot \Delta \phi_{\text{RES}-\text{IN}}$$

(2)

where,  $T_{OUT} = T_{IN} / M$ , is the period at the output of the PLL. Therefore, when a division by a factor M is inserted in the loop, the phase is divided by M considerably decreasing the phase resolution (when a M divider is used, the minimum output phase step becomes ( $360/2^k$ ) x M degrees). Actually, considering that  $\Delta \phi = \Delta \phi + m \cdot 2\pi$ , with m integer and that the relation between  $\Delta tRES$  and k is given by TIN/ $\Delta tRES = 2k$ , it is possible to choose M in order to have at the output the same resolution achievable at the input

$$\Delta \phi_{\text{RES}-\text{OUT}} = \Delta \phi_{\text{RES}-\text{IN}} + \mathbf{m} \cdot 2\pi \quad (3).$$

The value of M that allows to fulfill (3) is

$$M = m \cdot 2^k + 1 \qquad (4).$$

If (4) is respected, it is therefore possible to maintain at the output of the PLLs the same phase resolution imposed at the input by the digital block. Even though the M divider into the feedback path contributes to the overall phase noise of the PLL, the possibility to use this block with or without a mixer extends the applicability of the topology in different ranges of frequencies relaxing the design of the single blocks.

A further important step ahead in using the M divider instead of a mixer in the PLL is possible. The relation stated in (4) allows the use of an M divider but still imposes an important constraint on the choice of M and consequently, places some limitations in dimensioning the reference frequency given a wanted range of output frequencies. Actually, it is possible to overcome this problem. The basic idea is to use an odd value of M. Making this choice, it is possible to obtain at the output the same number of input phase shifts, that is the same phase resolution. The assumption generalizes the expression of M used in (2) as follows

$$M = m \cdot 2^k + n \quad (5)$$

with m and n integer numbers, with such a value of M, (2) can be rewritten as follows

$$\Delta \phi_{\text{RES}-\text{OUT}} = (m \cdot 2^{k} + n) \cdot \Delta \phi_{\text{RES}-\text{IN}} = n \cdot \Delta \phi_{\text{RES}-\text{IN}}$$

(6)

being  $\Delta \phi_{\text{RES-IN}}$  equal to  $2\pi/2^k$ , with

$$n = M \mod 2^k$$

(7).

The relation expressed in (6) states that the phase resolution at the output is n times the phase resolution at the input. Apparently (6) defines a coarse output resolution but this is not true. In fact,  $\Delta \phi_{\text{RES-OUT}}$  indicates only the output shift obtained relatively to the minimum input phase shift. Indeed, in this way the achievable 2<sup>k</sup> phase shifts are not still organized so that to the i-th input phase shift , i\* $\Delta \phi_{\text{RES-IN}}$ , corresponds the i-th output phase shift, i\* $\Delta \phi_{\text{RES-OUT}}$ , but if M is odd, then the output phase shifts are still equal to 2<sup>k</sup> solely, they are ordered in a different way. Assuming, L, the shift position, with  $0 < L < 2^k -$ 1, then results

$$\Delta \phi_{\text{OUT}} = \mathbf{n} \cdot \Delta \phi_{\text{IN}} = (\mathbf{n} \cdot \mathbf{L}_{\text{IN}} \cdot \Delta \phi_{\text{RES}-\text{IN}}) \mod 2\pi$$

(8)

where  $L_{IN}$  is the input position. It is possible to use the following relation

$$L_{OUT} = (n \cdot L_{IN}) \mod 2^{\kappa} \quad (9),$$

in order to know the output position  $L_{\text{OUT}}$  related to the input phase shift position.

The number of the output position,  $N_{OUT}$ , is the ratio between  $2^{k}$  and the Maximum Common Divisor (MCD) between M and  $2^{k}$ , denoted MDC(M,2k) as expressed in (10)

$$L_{OUT} = (n \cdot L_{IN}) \mod 2^k \quad (10)$$

As a consequence, it is clear that if M is an even number, some input positions are lost. Thus, the output phase resolution is coarser than the input phase resolution. On the contrary, if M is an odd number the phase positions are preserved and the phase resolution is maintained because the MCD between an odd number and a number that is a power of 2 is always 1.

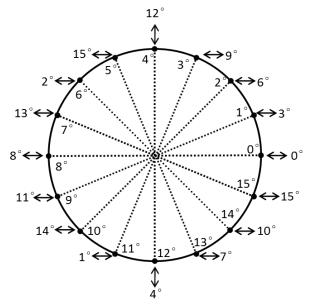

It is possible to visualize what happens when M is an odd number by using the phase wheel. In Fig. 5 on the phase wheel, the phase steps at the output (outside of the wheel) related to the phase steps at the input (inside of the wheel) assuming M equal to 19 and k equal to 4 (n=3) are reported. It is evident that the output phase steps are still 16 but distributed in a different way.

Fig. 5 The input (interior) and relative output (exterior) phase steps.

A first way to control the output phase position is to populate a Look Up Table (LUT) whose dimension must be  $N_{\text{OUT}}$  using (9) as follows

$$LUT(L_{OUT}) = (n \cdot L_{IN}) \mod 2^k, \ 0 < L_{IN} < 2^k - 1 \ (11).$$

Another solution inverts (9) implementing a simple algorithm which uses as input the factor used to know the output phase resolution in relation to the input phase resolution, n, the number of bit, k, the desired output resolution related to the input resolution, n'. The relation gives the multiplicative number, n'', used to determine which input position has to be imposed to obtain the desired output phase shift position. Such relation is:

$$n' = (n'' \cdot n) \mod 2^k, \ 0 < n'' < 2^k - 1$$

(12)

and the input position,  $L_{IN}$ , to be imposed is given by the following relation

$$L_{IN} = (n' \cdot L_{OUT}) \mod 2^k \quad 0 < L_{OUT} < 2^k - 1$$

(13)

A practical example is discussed in the section 4.

# B. The novel Phase Control Block

The proposed Phase Control Block is sketched in Fig. 3. This block has P outputs (the phase-shifted squared waves) and two inputs (the clock and the phase control words). It has two main sub-blocks: the counter and the bank of P comparators. The novel proposed PCB uses a counter as first sub-block instead of an accumulator unlike those reported in [24] and [25]. The use of an accumulator allows to change the frequency of the phase-shifted squared waves, thanks to an extra input called input word. However when the input word is greater than the unity the achievable phase-shift precision decreases and therefore to maximize the precision the input word should be set equal to one.

Actually since the output frequency is set by the PLLs, then the PCB can control the phase shifting independently from the output frequency. It is possible to maximize the phase-shift precision relaxing simultaneously the PCB in terms of complexity, and power consumption, by renouncing to the change of the frequency of the phase-shifted squared waves. The simple idea is to use the counter instead of the accumulator. Moreover the clock to the counter is provided by a PLL, then it is possible to recover the frequency variation of the phase-shifted squared waves by exploiting this PLL.

# IV. PROTOTYPES AND MEASUREMENTS

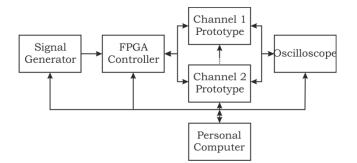

In order to validate the previous discussed advantages, a set of three prototypes has been built and measured. Each prototype is composed by two integer PLLs, a FPGA and a PC which handles the automatic phase and frequency switching of the prototype and the automatic measurements on the oscilloscope (Fig.6). The phase control block embedding the k-bit accumulator has been implemented on the FPGA, that provides the phase shifted signals to the inputs of the PLLs and the input phase words to the comparators, while the PLLs synthesize the desired outputs.

The external reference provided by a frequency generator, furnishes the clock for the phase control block and an oscilloscope has been used to measure the relative phase shifts between the PLLs. The PC governs the entire measurement setup. It is connected to the FPGA board and controls when the phase shift has to be changed. The PC is connected also to the PLLs and to the frequency generator in order to reprogram the PLLs when the reference frequency is changed, for the measurement on the entire VCOs bands. Finally, the PC controls the oscilloscope for the automatic measurement of the phase shifts. In detail the characteristics of the three prototypes are:

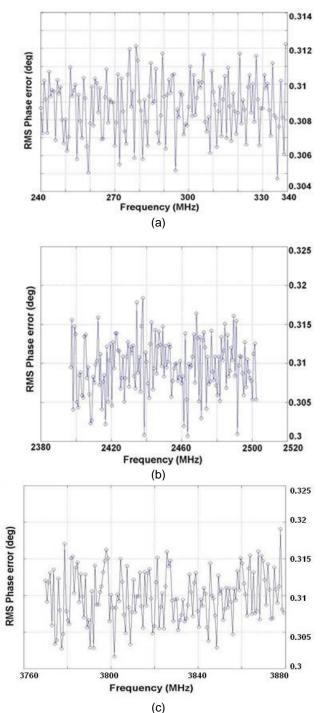

- 1. 1st prototype: center frequency= 290MHz, bit number=7, minimum phase shift =  $360^{\circ}/2^{7}$  =  $2.8125^{\circ}$ ;

- 2. 2nd prototype: center frequency=2.45GHz, bit number

= 7, minimum phase shift = 2.8125°;

- 3. 3rd prototype: center frequency=3.825GHz, bit number

= 6, minimum phase shift = 5.625°.

Fig. 6 Experimental setup used for prototypes measurements.

The overall bands of synthesis of the prototypes have been covered only by varying the external reference and reprogramming the PLLs.

The description of the three prototypes is similar, therefore, excluding the measurements, for reasons of space, only the case of the third prototype is reported in details. The value of M chosen is 2001, respecting (7) and (10); n is equal to 17 and  $N_{\rm OUT}$  is equal to 64. Being n different from the unity, it is necessary to ordinate the 64 output phase positions, then the algorithm previously described has been adopted using in (12) n'=1 and consequently n''=49. Thus, for example, to an output phase shift equal to 28.125°, respecting (9), the input position has to be 53. The entire PLL band has been characterized, starting from 3.77GHz to 3.88GHz with a step frequency of 0.733MHz. For each frequency, all the 64 positions have been measured and the results stored on the PC. Furthermore, the measures have been repeated, in different days, for ten times in order to test the repeatability and the reliability of the architecture.

The results are very good with a maximum absolute difference less than  $0.4^{\circ}$  between different measures. Fig. 7 shows the rms phase error calculated for each measured frequency in the VCO band and to facilitate the comparison also the rms phase error of the two other prototypes are shown. The third prototype exhibits a maximum rms phase error equal to  $0.3194^{\circ}$ , demonstrating the good phase accuracy over the entire measured band. In fact, thanks to the lock mechanism of the PLL the performances are uniform in the entire band of the VCO not only at its center band.

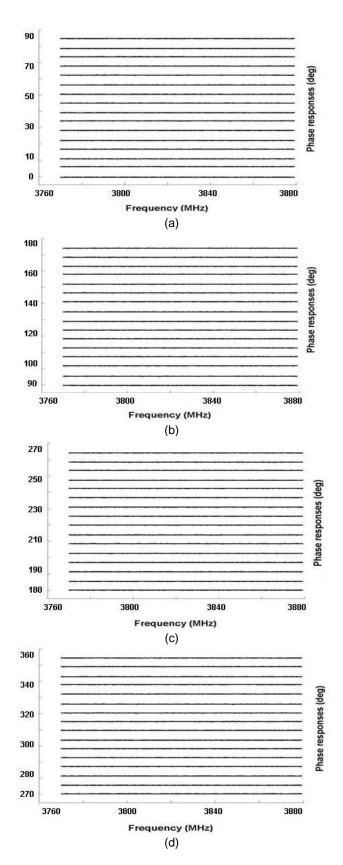

This feature is clearly shown by the results reported in Fig. 8(a), (b), (c) and (d) where the frequency responses of the phase shifter determined by the 6-bit digital input codes are shown. It's important to note the almost perfect parallelism of the curves, that demonstrates the frequency-independence of

the proposed architecture. The maximum peak-to-peak insertion phase calculated is about  $0.0979^{\circ}$ .

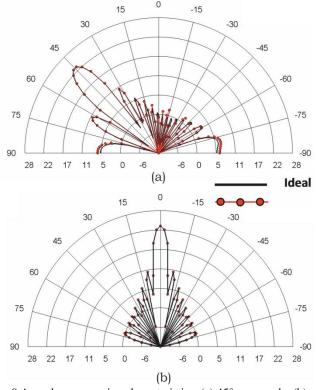

In order to underline the importance of the high resolution capability in different applications, in Fig. 9 are reported two cases of synthesized beam patterns (with an assumption of standard linear array with isotropic radiators and  $\lambda/2$  spacing between 16 elements). The radiation pattern related to the prototype has been evaluated using the measured 64 phase shifts at 3.8 GHz in Simulink<sup>®</sup>.

Fig. 8 Measured insertion phase of the 6-bit PS: (a) from 0° to 84.375°; (b) from 90° to 174.375°; (c) from 180° to 264.375°;(d) from 270° to 354.375°.

The ideal radiation pattern has been achieved considering an

ideal phase shifters. In both cases an assumption of the same power gain for all of the 16 elements has been made. It is possible to note the correct operation of the prototype. Moreover, it is evident that the reduction of the phase quantization error allows a reduction of the sidelobes, approaching the ideal case. This makes the proposed phased array transmitter suitable for instance to implement every technique of beamforming.

The rms phase errors of the other two prototypes have been also reported in Fig. 7. The achievable phase resolution basically depends on the rms phase error of the used PLL itself making the proposed architecture easily scalable in frequency. It is possible to note that the results are quite similar, showing better performances around 290 MHz. The measurements uncertainty has to be considered since the oscilloscope sampling rate has an important rule on this type of measurements in time domain. The lower is the output frequency of the PLLs, the better are the measurements and as a consequence the phase shift error evaluation. At the moment only for reason related on the measurement capabilities it is not possible to show prototypes working at higher frequencies.

Fig. 9 Array beam scanning characteristics: (a) 45° scan angle, (b) broadside scan at 3.8 GHz.

# V. CONCLUSION

An innovative phase shifter for high-resolution, continuous programmable phase shifts with the introduction of new concepts on using the M divider in the feedback loop of the PLL instead of the offset configuration has been discussed and experimentally validated. The prototypes reported have confirmed the outstanding results in terms of phase resolution and the scalability in frequency of the phase shifter. Due to the fact that they use as phase control block the FPGA it is not easy to quantify the equivalent power consumption imputable to the phase control block and therefore the prototypes cannot be used to estimate the power consumption.

The great flexibility of the proposed architecture grants that the frequency scalability is simply achieved by using a suitable PLL and the phase resolution is demanded to a very simple digital circuit.

The proposed topology is suitable for the implementation of any kind of digital beam forming and calibration technique in those applications which require continuous phase shifting, high resolution, and flexible and reprogrammable features.

# REFERENCES

- D. Parker and D.C. Zimmermann, "Phased arrays-Part II: Implementations, applications and future trends," IEEE Trans. Microwave Theory & Tech., vol. 50, no. 3, pp. 688-698, March 2002.

- [2] P.Lacomme, "New trends in airborne phased array radars," Proc. IEEE Int. Symp. Phased Array Systems and Technology, pp.17–22, Oct. 2003,.

- [3] A. Hajimiri, H. Hashemi, A. Natarajan, X. Guan, and A. Komijani, "Integrated phased array system in silicon," Proc. IEEE, vol. 93, no. 9,

- [4] pp. 1637–1655, Sep. 2005.

- [5] G.M Rebeiz, K.J. Koh,"Silicon RFICs for phased arrays," IEEE Microwave Magazine, vol. 10, no. 3, pp. 96-103, May 2009.

- [6] G. Perruisseau-Carrier, and A. K. Skrivervik, "Composite right/lefthanded transmission line metamaterial phase shifter (MPS) in MMIC technology," IEEE Trans. Microwave Theory & Tech., vol. 54, no. 4, pp. 1582-1589, April 2006.

- [7] M. A. Y, Abdalla, K. Phang, G.V. Eleftheriades," A planar electronically steerable patch array using tunable PRI/NRI phase shifters," IEEE Trans. Microwave Theory & Tech., vol. 57, no. 3, pp. 531-541, March 2009

- [8] L.A. Sanchez et al.,"An 8-Bit Digitally Controlled Programmable Phase Shifter Circuit for Sinusoidal Signals with 252° Phase Control Range, " In Circuits Syst Signal Process, vol. 32, pp. 415–431, 2013.

- [9] Y. Zheng C. Saavedra,"Full 360° vector-sum phase-shifter for microwave system applications, "In IEEE Trans. on Circ. and Systems-I, vol. 57 no. 4, pp. 752-758, 2009.

- [10] D. Viveiros, J. D. Consonni, and A. K. Jastrzebski, "A tunable all-pass MMIC active phase shifter," IEEE Trans. Microwave Theory & Tech., vol. 50, no. 8, pp. 1885-1889, August 2002.

- [11] S. Minaei, E. Yuce, "High Input Impedance NMOS-based Phase Shifter with Minimum Number of Passive Elements, "In Circuits Syst Signal Process, vol. 31, pp. 51–60, (2012).

- [12] H. Szu, R. Stapleton, and W. Willwerth, "Digital radar commercial applications," IEEE International Radar Conf., pp. 717-722, 2000.

- [13] H. Hashemi, X. Guan, A. Komijani and A. Hajimiri," A 24 GHz SiGe Phased-Array Receiver-LO Phase-Shifting Approach," IEEE Trans. Microwave Theory & Tech., vol. 53, no. 2, pp. 614-626, February 2005.

- [14] A. Natarajan, A. Komijani and A. Hajimiri," A fully integrated 24-GHz phased-array transmitter in CMOS," IEEE Journal of Solid-State Circuits, vol. 40, no. 12, pp. 2502-2514, December 2005.

- [15] S. Jeon, Y.J. Wang, F. Bohn, A. Natarajan, A. Babakhani and A. Hajimiri,"A scalable 6-to-18 GHz concurrent dual-band quad-beam phased array receiver in CMOS,"," IEEE Journal of Solid-State Circuits, vol. 43, no. 12, pp. 2660-2673, December 2008.

- [16] M. Gholami, "A Novel Low Power Architecture for DLL-Based Frequency Synthesizers, "In Circuits Syst Signal Process, vol. 32, pp. 781–801, 2013.

- [17] A. Bonfanti, D. De Caro, A, D. Grasso, S. Pennisi, C. Samori, A. G.M. Strollo," A 2.5-GHz DDFS-PLL with 1.8-MHz Bandwidth in 0.35-um CMOS," IEEE Journal of Solid-State Circuits, vol. 43, no. 6, pp. 1403-1413, June 2008.

- [18] A.W.H. Houghton, P.V. Brennan, "Phased array control using phaselocked-loop phase shifter," IEE Proceedingh-H, vol.139,no. 1, pp.31-37, February 1992.

- [19] N.B. Buchanan, V.F. Fusco, "Triple mode PLL antenna array, "IEEE MTT-S Digest, pp.1691-1694, 2004.

- [20] V. Fusco, N. Buchanan, (2009). Dual-mode retrodirective/phased array. In Electr. Letters, 45(3), 139-141.

- [21] H. Krishnaswamy, H. Hashemi, (2007). A 4-channel 24-27 GHz UWB phased array transmitter in 0.13 um CMOS for vehicular RADAR. In Proc. of IEEE Custom Integrated Circuit Conf., 753-756.

- [22] G. Avitabile, F. Cannone, A. Vania, "Phase Shifter based on DDS Driven offset-PLL," Electronics Letters, Vol. 42, No. 25, pp. 1438-14397, December 2006.

- [23] G. Avitabile, F. Cannone, G. Coviello, "Low-Power Tx module for highresolution continuous programmable phase shift," Electronics Letters, Vol. 44, No. 18, pp. 1052-1054, August 2008.

- [24] F. Cannone, G. Avitabile, G. Coviello,"A novel 2.4GHz High-resolution and low-power phased array transmitter," Proc. of European Microwave conf., pp. 1022-1025, October 2009.

- [25] C.T. Charles, D.J. Allstot, "A calibrated phase and amplitude control system for a 1.9 GHz phased-array transmitter element," IEEE Trans. on Circuits and Systems, accepted for future publication.

- [26] K.J. Koh, J.W. May, G.M. Rebeiz, "A millimeter-wave (40-45 GHz) 16element phased-array transmitter in 0.18-um SiGe BiCMOS technology," IEEE Journal of Solid-State Circuits, vol. 44, no. 5, pp. 1498-1509, May 2008.

- [27] L. Li, W. Hong, Y. Zhang, Z. Chen, P. Chen, "Design and Implementation of an Active Array Antenna With Remote Controllable Radiation Patterns for Mobile Communications," In IEEE Trans. om Ant. Propag. Vol. 62 no. 2, pp. 913-921, 2014.