# Design and Performance Evaluation of Energy Efficient 8-Bit ALU At Ultra Low Supply Voltages Using FinFET With 20nm Technology

V. Vijay, Sadulla Shaik, P. Chandra Shekar, P. Manoja, R. Abhinaya, M. Rachana, N. Nikhil

Abstract—Since last few years, the tiny size of MOSFET, that is less than tens of nanometers, created some operational problems such as increased gate-oxide leakage, amplified junction leakage, high sub-threshold conduction, and reduced output resistance. To overcome the above challenges, FinFET has the advantages of an increase in the operating speed, reduced power consumption, decreased static leakage current is used to realize the majority of the applications by replacing MOSFET. By considering the attractive features of the FinFET, an ALU is designed as an application. In the digital processor, the arithmetic and logical operations are executed using the Arithmetic logic unit (ALU). In this paper, power efficient 8-bit ALU is designed with Full adder (FA) and multiplexers composed of Gate diffusion input (GDI) which gained designer's choice for digital combinational circuit realization at minimum nower consumption. The design is simulated using Cadence virtuoso with 20nm technology. Comparative performance analysis is carried out in contrast to the other standard circuits by taking the critical performance metrics such as delay, power, and power delay product (PDP), energy-delay product (EDP) metrics into consideration.

*Keywords*—8-bit ALU, EDP, FinFET, Full Adder, GDI, PDP, Static leakage current.

#### I. INTRODUCTION

THE Very Large Scale Integration (VLSI) is the task of designing an Integrated circuit by clubbing thousands of

V. Vijay is with the Department of Electronics and Communication Engineering, Institute of Aeronautical Engineering, Hyderabad-500043, India (phone: 040-29705852; e-mail: v.vijay@iare.ac.in).

Sadulla Shaik is with the Department of Electronics and Communication Engineering, Vignan's Foundation for Science, Technology & Research, Unviersity,Vadlamudi-522213, India (e-mail: sadulla09@gmail.com).

P. Chandra Shekar is with the Department of Electronics and Communication Engineering, MLR Institute of technology, Hyderabad-500043, India (e-mail: chandu.p4u@mlrinstitutions.ac.in).

P. Manoja is with the Department of Electronics and Communication Engineering, Institute of Aeronautical Engineering, Hyderabad-500043, India (e-mail: puttamanoja@gmail.com).

R. Abhinaya is with the Department of Electronics and Communication Engineering, Institute of Aeronautical Engineering, Hyderabad-500043, India (e-mail: rallabhandy.abhinaya994@gmail.com).

M. Rachana is with the Department of Electronics and Communication Engineering, Institute of Aeronautical Engineering, Hyderabad-500043, India (e-mail: merugurachana1997@gmail.com).

N. Nikhil is with the Department of Electronics and Communication Engineering, Institute of Aeronautical Engineering, Hyderabad-500043, India (e-mail: n.nikhil020296@gmail.com).

transistors into one chip. The VLSI turned up in the year 1970 when the complex Semiconductor and Communication technologies were being emerged. The electronics industry achieved a considerable expansion over the last few decades, mainly because of the rapid promotions in the large scale integration technologies and the applications of system design. With the advantages of the VLSI designs, the implementation of ICs in communications, video and image processing has been rising. Even for no portable devices, power consumption is an essential criterion due to raising in the packaging and cooling costs along with reliability issues. Considering these problems, the primary challenge for the design engineers is inadequate, realization within a targeted power without compromising the performance requirement [1].

The tiny size of the MOSFET, less than tens of nanometers, created some operational problems such as high sub-threshold conduction which means; in the MOSFET, the applied voltage to gate terminal is to be decreased to maintain the reliability [2]-[3]. Then the threshold voltage which is to be applied to the MOSFET must also be reduced. As this threshold voltage is decreased possibly to a very great extent, the transistor will not be able to switch from the complete turn-off to complete turn-on state and vice versa. The rise of gate-oxide leakage refers to the gate oxide, serving as an insulator in between the channel and gate must be designed as thin as possible in order to elevate the conductivity of the channel and performance of the device when it is in ON state and to decrease the subthreshold leakage during OFF state of the device. The increased junction leakage means the design of junction becomes quite more difficult in smaller devices, leading to higher doping levels which lead to drain induced barrier lowering. And many more drawbacks such as lower output resistance, lower transconductance.

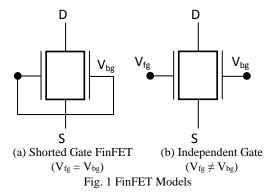

The scaling of gate lengths to very short distances is possible with FinFET technology. FinFET-DGCMOS and conventional CMOS fabrication are similar to one another, except negligible disturbances, allows the participation of more efforts in the significant involvement of the yielding the applications. FinFET channel is a un-doped structure of smaller in size portion which is placed in a perpendicular direction to that of substrate terminal. Coulomb scattering is eliminated by un-doped channel because of faster mobility in FinFETs by the unwanted impurities [4]. The two gates of the FinFET are provided to control the short channel effects without aggressively scaling down the gate-oxide thickness and increasing the channel doping density. In terms of the structure of FinFET, it is a double gate device, and the gates are formed at the vertical side of the fin using a thin gate oxide layer. Fin is a thin layer between the source and drain. FinFET reduces the levels of the leakage current and mitigates the short channel effects [5]. In this paper, the reduction in power consumption by scaling down the size of a transistor in nanoelectronics with the help of FinFET is achieved.

This paper mainly focuses on the implementation of 8-bit ALU using FinFET with 20nm technology. ALU is the core part of the central processing unit and is a combinational digital electronic circuit which accomplishes all the logical and arithmetic operations. Arithmetic modules provide minimum energy consumption at extended reliability plays a crucial role in the die. Thereby, the design changes in the ALU reflect a significant effect on the overall performance of the whole processor. To meet the reduced energy consumption and increased speed of ALU, designs require arithmetic, circuit and system level methodologies involvement [6]. Even much of the logic styles viz. clock gating, frequency, and voltage scaling are producing the minimum power consumption applications, but few amongst those are offering improved power consumption factor with the optimized die size [7].

The emerging features in the new era of integrated circuit (IC) are driven with the modern days' technological advancements in the processing of silicon technology. With the revolutionary change in the realization of commercial ICs, the chip development foundries are producing the highly complex, enhanced reliability, minimum energy consumption, and more robustness processors. The central processing unit (CPU) is the basic module inside the microprocessor and composed with the ALU as a primary module. The key operations of the ALU are both arithmetic and logical operations. The arithmetic operations of addition, subtraction, multiplication and division are performed as addition, inverted addition, recursive addition, and recursive inverted addition, respectively. The majority of the addition operations in the digital system are formed using the full adder, and the major constraint in the full adder design is to produce the circuits with minimum energy dissipation, less delay, energy efficiency in addition to reliability feature [8]. In contrast to the existed MOSFET designs, the novel innovation of FinFET models is considered to implement the full adder with the improved parameters of both device and energy efficiency. The 8-bit ALU is developed using Full adder and Multiplexers which are composed by using gate diffusion input (GDI) technique.

The remaining paper is organized as follows: The FinFET characteristics and modeling are discussed in section II concerning their structural behavior. Section III elaborated the design of proposed 8 bit ALU blocks using FinFET spectre models in cadence virtuoso environment. The functional verification of the constructed circuits has presented in section IV with the relevant simulation results. And finally, the

conclusion is given in section V regarding the fulfillment of primary objectives.

#### II. FINFET CHARACTERISTICS AND MODELING

FinFET has got the name as such because of the Field effect transistor (FET) with a structure that view as a set of fins when gazed. It consists of a conducting region, which mainly surrounded with the thin 'fin' structure and is built on silicon

on insulator by which the name 'FinFET' is evolved. The device channel for effective conduction is calculated with the fin thickness.

The FinFET is a non-planar device; double gate transistor, which is either a bulk Silicon-On-Insulator (SOI) or on Silicon Wafers [2]-[9]. This is importantly based on single gate transistor design. There are two different types of FinFET. They are Bulk FinFET and SOI FinFET. The critical characteristic of the FinFET is that it has a conducting channel that is bounded by a thin silicon fin [10]. This mainly forms the body of the device. These fins are nothing but the channel between the source and drain. The gate terminal is bounded around the channel. This lets the formation of the several gate electrodes to reduce the leakage current and to improve the drive current [11]-[12].

The FinFET works the same as that of Conventional MOSFET. It operates in two modes: Enhancement mode and Depletion mode. The working characteristics are identical in both modes, but the only difference is that, in the enhancement mode, if no voltage is given to the gate terminal, it doesn't conduct whereas in the depletion mode, if the voltage is applied to the gate, it doesn't conduct. In the enhancement mode when the voltage is applied to the gate terminal, a parallel plate capacitor is formed. The gate is made up of the oxide layer. The surface below the oxide layer is located between the source and drain. When a small amount of positive voltage is applied to the gate concerning the source, a depletion region is formed. This region is reversed to n-type by the applied positive voltage. Then a region is formed at the interface between Si and SiO2. This applied positive voltage attracts the electrons from the source terminal to the drain terminal. By this, an electron reach channel is formed. The flow of current starts by applying a voltage between the source and drain. This flow of current is dependent on the voltage applied to the gate.

'D.' The below table 2 shows the functionality of 4x1 MUX.

The advantages and applications of FinFET are, it consumes very less power that allows higher integration levels [13]. It operates at the lower voltages as the threshold voltage given is less. The FinFET has passed the barrier of 20nm which was previously a barrier. The static leakage current has been reduced up to 90% when compared to that of traditional methods, and its operational speed has been increased up to 30% than non FinFET devices. Samsung Electronics has incorporated FinFET in its 14nm process. Along with Samsung, Apple, Intel and Taiwan Semiconductor Manufacturing Company (TSMC) are set to ship the 14nm technology, which is a benefit to all smart phones as it will speed with the phone.

#### III. PROPOSED 8 BIT ALU BLOCK USING FINFET MODELS

Apart from the traditional CMOS design, the GDI technique is another low power and area efficient technique [14]. The aim of the GDI technique is to improve the performance of logic circuits [15]. A common GDI cell comprises of four terminals. They are P (PMOS outer diffusion node), G (Common gate input for both PMOS and NMOS transistors), D (Common diffusion for both the transistors), N (NMOS outer diffusion node).

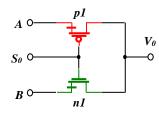

### A. GDI based Multiplexer

GDI based logic is used to implement 2:1 MUX whose function is based on the use of a simple cell. When the select line is fed with '0' the output will be the data 'A.' And when select line is fed with '1' the output will be the data 'B.' The below truth table shows the functionality of the 2x1 Multiplexer.

Fig. 2 Design of 2x1 Multiplexer

| Table 1 the truth table of $2x1$ | Multiplexer |

|----------------------------------|-------------|

|----------------------------------|-------------|

| Select line | $V_0 = \overline{S_0}A + S_0B$ |

|-------------|--------------------------------|

| $S_0$       | Y                              |

| 0           | А                              |

| 1           | В                              |

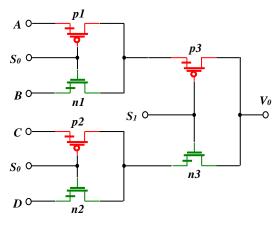

GDI based logic is to implement 4:1 MUX whose function is based on the use of a simple cell. When the select line S0 is fed with '0' the output will be the data 'A' or 'C.' And when select line S1 is fed with '1' the output will be the data 'B' or

Fig. 3 Design of 4x1 Multiplexer

Table 2 the truth table of 4x1 Multiplexer

| Sele  | ct line | Output                                                                                 |  |

|-------|---------|----------------------------------------------------------------------------------------|--|

| $S_0$ | $S_1$   | $V_0 = \overline{S_0 S_1} A + \overline{S_0} S_1 B + S_0 \overline{S_1} C + S_0 S_1 D$ |  |

| 0     | 0       | А                                                                                      |  |

| 0     | 1       | С                                                                                      |  |

| 1     | 0       | В                                                                                      |  |

| 1     | 1       | D                                                                                      |  |

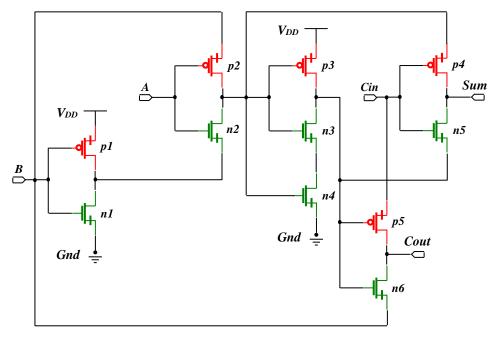

## B. 11T Full Adder

A full adder is a fundamental requisite to design an ALU. The 11T methodology is used for developing Full Adder; this is another way of designing Full Adder to reduce power and delay. Full Adder is depicted in Fig. 4. This circuit operates at very low voltages such as less than 1V. This circuit is driven with a supply voltage of 0.9 (Vdd). The Input A is given to the gate of the terminal of p1, n1 and drain terminal of p2. Input B is applied to the gate terminals of the transistors p2 and n2 and the drain terminal of the n1. The passage of the signal occurs from gate to drain terminal during the ON condition of, and it became possible when the applied voltage (Vs) is higher to that of threshold voltage (Vth). That means the voltage is passed from gate to drain. So, when the Input A is high, it gives the signal applied to the terminal B. Full Adder is built using low power EX-OR gates and 2×1 Multiplexer. The outputs of 'Sum' and 'carry' (Cout) are obtained from EX-OR and Multiplexer circuits, respectively. Additional transistor numbered as n6 takes minimum power as it is driven with the ultra-low mode in combination with the sub-threshold current. The voltage across the gate to source (VGS) become higher to that of threshold voltage (VTH) because of strong inversion

region, and this leads to accumulating minority charge carriers by vanishing the majority charge carriers. The subthreshold current being generated because of leakage current by the deployment of minority charge carriers during the case of the weak inversion region of VTH is greater than VGS. The required operation of the circuit is met with sufficient current which is gained from the subthreshold current at VDD value is lower than the VTH. The resultant current gives the circuit to operate with ultra-low mode by consuming minimum power. Successful operation of 11T full adder is achieved with an additional transistor, n6 at the subthreshold mode.

Fig. 4 Design of 11T Full Adder

| Table 3 the truth | table of 4x1 | Multiplexer |

|-------------------|--------------|-------------|

|-------------------|--------------|-------------|

| Input |   |     | Output |      |  |

|-------|---|-----|--------|------|--|

| А     | В | Cin | Sum    | Cout |  |

| 0     | 0 | 0   | 0      | 0    |  |

| 0     | 0 | 1   | 1      | 0    |  |

| 0     | 1 | 0   | 1      | 0    |  |

| 0     | 1 | 1   | 0      | 1    |  |

| 1     | 0 | 0   | 1      | 0    |  |

| 1     | 0 | 1   | 0      | 1    |  |

| 1     | 1 | 0   | 0      | 1    |  |

| 1     | 1 | 1   | 1      | 1    |  |

Table 4 the truth table of 11T Full Adder

| S     | elect Line | es             |             |        |  |

|-------|------------|----------------|-------------|--------|--|

| $S_2$ | $S_1$      | $\mathbf{S}_0$ | Operation   | Output |  |

| 0     | 0          | 0              | AND         | 0      |  |

| 0     | 0          | 1              | INCREMENT   | 1      |  |

| 0     | 1          | 0              | OR          | 1      |  |

| 0     | 1          | 1              | DECREMENT   | 0      |  |

| 1     | 0          | 0              | SUBTRACTION | 1      |  |

| 1     | 0          | 1              | XOR         | 0      |  |

| 1     | 1          | 0              | SUBTRACTION | 0      |  |

| 1     | 1          | 1              | ADDITION    | 1      |  |

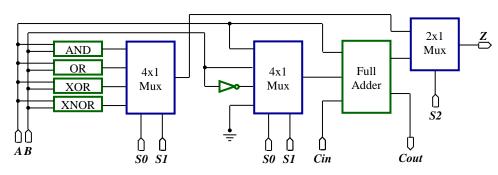

#### C. 1-Bit & 8- Bit ALU

For any input over the input terminals A, B and C the ALU perform arithmetic and logical operations depending on the input given over the select line. The ALU is a part of the processor that tackles all the arithmetic and logical operations as it is named.

The above truth table shows the operations performed by the ALU depend on 3 Bit select line giving eight conditions. Let the input A is driven with logical '0', B with logical '1' and C with logical '1'. The Logical AND operation is performed when the select line S2 is fed with logical '0', S1 logical '0' and S0 as logical '0'. The ALU is INCREMENTED from its present state when the select line S2 is driven by logical '0', S1 with logical '0' and S0 logical '1'. The operation Logical OR is implemented when S2 is fed with logical '0', S1 logical '1' and S0 as logical '0'. DECREMENT operation is carried out when select line S2 is fed with logical '0', S1 logical '1' and S0 with logical '1'. The SUBTRACTION operation turns up for the applied signal over select line S2 is logical '1', S1 is logical '0', and S0 is logical'0'. For the Logical EX-OR operation the select line S2 is to be fed with logical '1', S1 logical '0' and S0 logical '1'. The Logical EX-NOR operation is accomplished when the select line S2 is fed with logical '1', S1 with logical '1' and S0 with a logical '0'. That which is last, the ADDITION operation is carried out for S2 is fed with logical '1', S1 with logical '1' and S0 with logical '1'.

Fig. 5 Block Diagram of 1-Bit ALU [16]

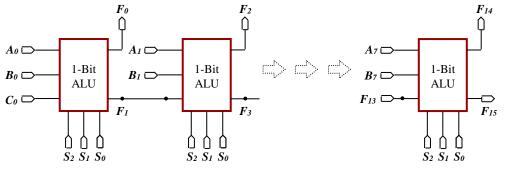

Fig. 6 Block Diagram of 8-Bit ALU

For the 8-Bit ALU shown in Fig. 6, A, B, and C are Inputs of ALU. S0, S1 as S2 are 3-bit selection lines. F0 and F1 are Output of 1-bit ALU. F14 is the output of 8-Bit ALU, and F15 is carry obtained for last Full adder [16]-[17].

For any input over the input terminals A, B, and C, the ALU performs arithmetic and logical operations depending on the input given over the select line. The 8-bit ALU is obtained by cascading all 1-Bit ALU's [18]-[20]. The above block diagram shows the cascaded form of all 1-Bit ALU's. The carry which is obtained for the first Full adder's ALU is forwarded to the next Full adder's ALU. This process is continued to last ALU to form an 8-bit ALU.

#### IV. SIMULATION RESULTS AND EXPERIMENTAL FINDINGS OF THE PROPOSED WORK

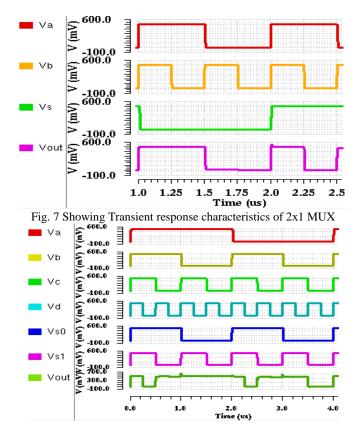

The circuit is shown in Fig. 2 and Fig. 3 are simulated using the Cadence virtuoso tool by considering the FinFET technology spectre files. The voltage applied to the proposed circuit is 600mv or 0.6 V which falls under the operating voltage range of the FinFET. The multiplexers are designed using Gate Diffusion Input (GDI) technique which is advantageous in the field of reducing the circuit area and the supply voltage. The output (Vout) is obtained depending on the selection lines (Vs), (Vs0) and (Vs1) for both the multiplexers. When (Vs) is given with 0V the input 'A' is passed to the output and when (Vs) is given with 0.6 V then 'B' is passed to the output. Similarly, when (Vs0) is applied with 0 V the input 'A' and 'C' are passed to the next level, for (Vs1) when applied with 0.6 V, input 'B' and 'D' is passed to the next level. Depending on data over terminal Vs1 the inputs 'A', 'B,' 'C' or 'D' as passed over the output terminal. The simulated output of Fig. 2 and Fig. 3 are shown in Fig. 7 and Fig. 8, respectively.

# INTERNATIONAL JOURNAL OF SYSTEMS APPLICATIONS, ENGINEERING & DEVELOPMENT DOI: 10.46300/91015.2020.14.10

Fig. 8 Showing Transient response characteristics of 4x1 MUX

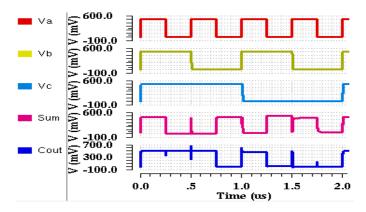

Full Adder using 11T is shown in Fig. 4. Is simulated using the Cadence Virtuoso tool by considering the FinFET technology spectra files. Moreover, its simulated output is shown in Fig. 9.

Fig. 9 Showing Transient response characteristics of 11T Full Adder

The 11T Full Adder operates in ultra-low mode by consuming minimum power. The voltage applied to the proposed circuit is 600mv or 0.6 V. The Full Adder is responsible for the three-bit addition, whereas Half Adder can only add two bits and neglects the carry which is obtained. The input (Vc) is added along with the bits with (Va) and (Vb) which is the carry output obtained from the circuit itself.

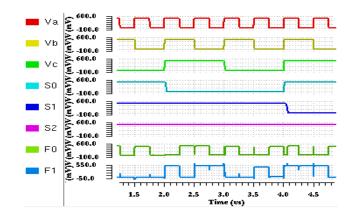

Fig. 10 Showing Transient response characteristics of 1-Bit ALU The simulation of 1-Bit ALU shown in Fig. 5. is carried out and the simulated output is depicted in Fig. 10. The proposed circuit operates with a voltage of 0.6 V or 600mv. The response consists of eight different operations, which are the combination of arithmetic and logical operations and these operations depend on the input given over the selection lines (S0), (S1) and (S2). The (F0) is the output of the 1-Bit ALU as shown in Fig. 10 and (F1) is the input which is applied to the ALU during cascading.

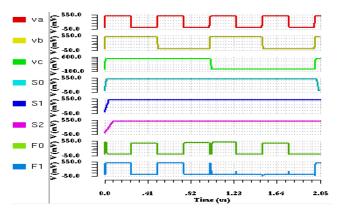

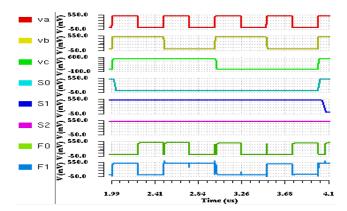

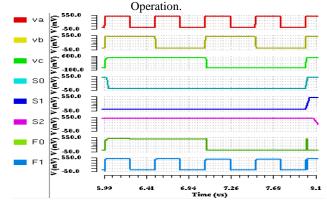

Fig. 11 (a). Showing Transient response characteristics of AND Operation

Fig. 11 (b). Showing Transient response characteristics of OR Operation

Fig. 11 (c). Showing Transient response characteristics of EX-OR

Fig. 11 (d). Showing Transient response characteristics of EX-NOR Operation

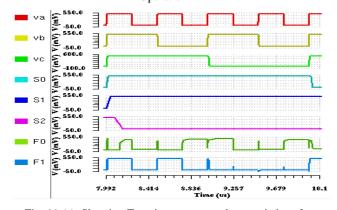

Fig. 11 (f). Showing Transient response characteristics of

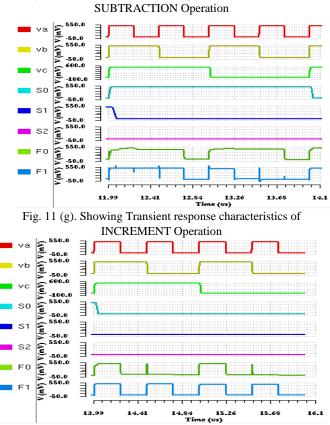

Fig. 11 (h). Showing Transient response characteristics of DECREMENT Operation

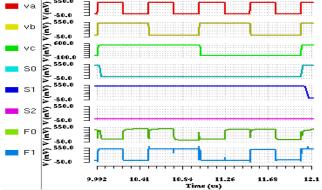

The above are the transient responses of 8 individual operations performed by the 1-Bit ALU. The ALU yields eight different operations in which four are arithmetic, and four are logical operations depending on the select line. The sub-figures in Fig. 11 shows the different operations of the 1-Bit ALU for the supply voltage of 0.6V. The role of selection line which is about three bit plays a vital role in delivering the output responses which are as follows.

The Fig. 11 (a) shows, Logical AND operation when the select line S2 is fed with logical '0', S1 logical '0' and S0 as logical '0'. The ALU is INCREMENTED from its present state when the select line S2 is driven by logical '0', S1 with logical '0' and S0 logical '1' as shown in Fig. 11 (g). The Logical OR Operation as shown in (b) is implemented when S2 is fed with logical '0', S1 logical '1' and S0 as logical '0'. The DECREMENT operation is carried out when select line S2 is fed with logical '0', S1 logical '1' and S0 with logical '1' as depicted in Fig. 11 (h). As shown in Fig. 11 (f) SUBTRACTION operation turns up for the applied signal over select line S2 is logical '1', S1 is logical '0', S0 is logical '0'. For the Logical EX-OR operation in Fig. 11 (d) the select line S2 is to be fed with logical '1', S1 logical '0' and S0 logical '1'. The Logical EX-NOR operation is accomplished when the select line S2 is fed with logical '1', S1 with logical '1' and S0 with a logical '0' as shown in Fig. 11 (c). Also, Fig. 11 (e) shows the ADDITION operation is carried out for S2 is

4.5

4.0 Time

**'**1'. () ₩ -50.0 ₩ 550.0 Va A 5-A 50.0 A 550.0 A 550.0 ∃ Vb م 550.0 ق -50.0 ∃ Vc 550.0 ≣ SO E -50.0 550.0 S1 )۔ 2 550.0 A 550.0 H -50.0 A 550.0 S2 A(Am) ∃

F14

-50.0 550.0 Ň. F15

-50.0

∃

3.0

fed with logical '1', S1 with logical '1' and S0 with logical

3.5

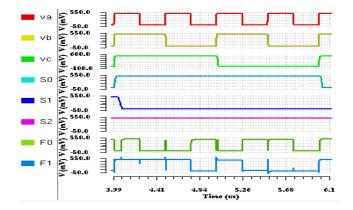

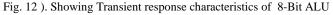

The simulated output of 8-Bit ALU as shown in Fig. 12 is obtained by simulating the circuit shown in Fig. 6. The voltage applied to the proposed circuit is 0.6 V. The same selection input is applied to all the 1-Bit cascaded ALU's along with the supply voltage. For the different inputs over the selection line, the proposed circuit performs eight different operations, including four arithmetic and four logical operations.

Table 5 shows the obtained results by simulating the 8-bit ALU using FinFET in the cadence virtuoso tool. The 8-bit ALU is designed using Full adder and multiplexers. The key metrics of power, delay, PDP as well as EDP are analyzed for multiplexers, Full adder, 1-bit ALU and for 8-bit ALU.

| Design               | Delay  | Power | PDP     | EDP   |

|----------------------|--------|-------|---------|-------|

|                      | (nS)   | (nW)  | (aJ)    | (yJs) |

| Full adder           | 0.0044 | 3.6   | 0.01584 | 69.7n |

| GDI based 2×1<br>MUX | 0.0013 | 9.9   | 0.01287 | 16.6n |

| GDI based 4×1<br>MUX | 8.1    | 19    | 153.9   | 1.25  |

| 1-Bit ALU            | 2.17   | 26.8  | 58.15   | 0.13  |

| 8-Bit ALU            | 1.97   | 200   | 394     | 0.78  |

Table 5 Analysis of Power, Delay, PDP and EDP

The results show that the power consumed for the Full adder is 3.6nW, GDI based 2×1 MUX, and GDI based 4×1 MUX is 9.9nW and 19nW, respectively. For the 1-bit ALU it is 26.8nW and 8-bit ALU it is 0.2µW. The delay metrics calculated for Full adder is 4.4ps, GDI based 2×1 MUX, and GDI based 4×1 MUX is 1.3ps and 8.1ns, respectively. For the 1-bit ALU and 8-bit ALU, the delay metrics are 2.17ns and 1.97ns. The product of power and delay is the standard performance parameter which is taken into consideration when

comparing standard circuits. The PDP for Full adder is 15.84nW\*ps, GDI based 2×1 MUX is 12.87nW\*ps and GDI based 4×1153.9nW\*ns, 1-bit ALU and 8-bit ALU are 58.15nW\*ns and 0.394µW\*ns, respectively. The product of energy and delay is also another significant factor which is to be measured. The energy-delay product for Full adder is 69.6J\* nW\*ps, GDI based 2×1 MUX is 16.731J\* nW\*ps, and GDI based 4×1is 1246.59J\* nW\*ns, 1-bit ALU and 8-bit ALU are 126.198J\* nW\*ns and 0.776J\* uW\*ns, respectively.

#### V. CONCLUSION

In this paper, the 8 bit ALU is designed using GDI based 4×1 & 2×1 multiplexers and a Full adder. As CMOS has some operational problems like short channel effects which include Drain-induced barrier lowering, high sub-threshold conduction, increased gate oxide leakage, increased junction leakage, lower output resistance. To overcome the above problems, CMOS is replaced with FinFET. ALU represents the fundamental building block of the central processing unit of a computer, and modern CPUs contains mighty and complex ALU. It performs arithmetic operations, which includes addition, subtraction, increment, decrement, and logical operations, which includes OR, AND, XOR and XNOR. The required gates for these operations are designed using FinFET, and a multiplexer performs logical operations. Here, the power consumption, circuit's delay, in addition to their PDP along with EDP are analyzed which gave the quite better values in terms of power and delay when compared to CMOS technology. The delay of 8-bit ALU is minimized to 1.97ns from 6.95ns and the power consumption reduced to 0.2µwatts from 32µwatts when compared to that of CMOS technology. The FinFET based circuit gave the required output by reducing the delay, power consumption at ultra-low supply voltages.

#### REFERENCES

- [1] Shiva Taghipour, and Rahebeh Niaraki Asli, "Aging comparative analysis of high-performance FinFET and CMOS flip-flops," Microelectronics Reliability, vol. 69, iss. 2, 2013, pp. 52-59.

- [2] Osama Abdelkader, Mohamed Mohie El-Din, Hassan Mostafa, Hamdy Abdelhamid, Hossam A. H. Fahmy, Yehea Ismail, and Ahmed M. Soliman, "Technology Scaling Roadmap for FinFET-Based FPGA Clusters Under Process Variations," Journal of Circuits, Systems and Computers, vol. 27, iss. 4, 2018, pp. 1850056(1-32).

- A. Jain, and M. Saxena, "Optimization of leakage Current and leakage [3] Power of FinFET Based 6T SRAM Cell," International Journal of Engineering Technology, Management and Applied Sciences, vol. 2, iss. 3, 2014, pp. 156-163.

- X. Lin, Y. Wang, and M. Pedram, "Stack Sizing Analysis and [4] optimization for FinFET Logic cells and circuits operating in the sub or near threshold regime," 15th International Symposium on Quality Electronic Design Santa Clara, CA, USA, March 3-5, 2014, pp. 341-348

- [5] Sadulla Shaik, K. Sri Rama Krishna, and Ramesh Vaddi, "Nano-Scale Transistors with Circuit Interaction for Designing Energy- Efficient and Reliable Adder Cells at Low VDD," IETE Technical Review, Vol. 35, No. 5, 2018, pp. 456-466.

- [6] D. Nirmal, P. Vijaya Kumar, and S. Jabaraj, "NAND Gate Using FinFET for Nano Scale Technology," International Journal of Engineering Science and Technology, vol. 2, iss. 5, 2010, pp. 1315-1358.

- [7] Aminul Islam, M. W. Akaram, and M. Hasan, "Energy Efficient and Process Tolerant Full Adder in Technologies Beyond CMOS," Int. J. on Recent Trends in Engineering & Technology, vol. 5, iss. 1, 2011, pp. 60–68.

- [8] Sadulla Shaik, K Sri Rama Krishna, and Ramesh Vaddi, "Tunnel Transistors with Circuit Co-Design in Designing Reliable Logic Gates for Energy Efficient Computing" IEEE Asia Pacific Conference on Post Graduate Research in Microelectronics and Electronics (Prime Asia-2015). On 27th to 29th November 2015, pp. 306-311.

- [9] Alak Majumder, and Pritam Bhattacharjee, "Variation aware intuitive clock gating to mitigate on-chip power supply noise," International Journal of Electronics, just accepted, 2018].

- [10] Wei Lim, Huei Chaeng Chin, Cheng Siong Lim, and Michael Loong Peng Tan, "Performance evaluation of 14nm FinFET-based 6T SRAM cell functionality for DC and transient circuit analysis," Journal of Nanomaterials, vol. 2014, pp. 1–8.

- [11] A.N. Moulai Khatir, A. Bouazza, and B. Bouazza, "Corner Effects Sensitivity to Fin Geometry Variations in tri-gate SOI-FinFET," Journal of Electronics Devices, vol. 18, 2013, pp. 1549–1552.

- [12] M. Onabjo, and J.S. Martinez, "Process Variation Challenges and Solutions Approaches," Analog circuit design for process variationresilient systems-on-a-chip, Springer, Boston, MA, 2012, pp. 9–30.

- [13] Sadulla Shaik, K. Sri Rama Krishna, and Ramesh Vaddi, "Tunnel Transistor-Based Reliable and Energy Efficient Computing Architectures with Circuit and Architectural Co-Design at Low VDD," Journal of Circuits, Systems, and Computers, Vol. 27, No. 3, 2018, pp. 1850046- (1–21)..

- [14] Vinay Kumar, Ravindra kumar Shrivatava, and Madhav Mansukh Padaliya, "A Temperature Compensated Read Assist for Low Vmin and High Performance High Density 6T SRAM in FinFET Technology," 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), Pune, India, Jan. 6-10, 2018, pp. 447–448.

- [15] D. Akshay, K. Abhilash, and K.D. Sandeep, "Design and Implementation of Area Optimized ALU Using GDI Technique," International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering, vol. 2, iss. 3, 2014, pp. 1169– 1172.

- [16] Anagh Deshpande, and T. Vigneswaran, "Design of Arithmetic and Logic Unit (ALU) Using Subthreshold Adiabatic Logic for Low-Power Application," VLSI Design: Circuits, Systems and Applications, Springer, Singapore, 2018, pp. 201–209.

- [17] T.E. Rani, M.A. Rani, R. Rao, "AREA optimized low power arithmetic and logic unit," 2011 3rd IEEE international conference on Electronics Computer Technology (ICECT), Kanyakumari, India, April 8-10, 2011, pp. 224–228.

- [18] Polani Rahul, Korada Prudhvi Raj, and S. Umadevi, "8-Bit Asynchronous Wave-Pipelined Arithmetic Logic Unit," Nanoelectronic Materials and Devices, Springer, Singapore, 2018, pp. 233–243.

- [19] Subramanyam, Kasturi, Sadulla Shaik, and Ramesh Vaddi. "Tunnel FET based low voltage static vs dynamic logic families for energy efficiency." VLSI Design and Test, 18th International Symposium on VDAT-14. IEEE, 2014, pp. 1-2.

- [20] P. Ghosh, T. Saha, and B. Kumari, "Aspects of Low-Power High-Speed CMOS VLSI Design: A Review," Industry Interactive Innovations in Science, Engineering and Technology, Springer, Singapore, 2018, pp. 385–394.

Vallabhuni Vijay (SM'13–M'17) received the B.Tech degree in electronics and communication engineering from Jawaharlal Nehru Technological University, Kakinada in 2009, M.Tech degree in VLSI design from Vignan's Foundation for Science, Technology & Research, Vadlamudi in 2011, Ph.D degree from Vignan's Foundation for Science, Technology & Research, Vadlamudi in 2017. He is presently working as an associate professor in the Department of Electronics & Communication Engineering at Institute of Aeronautical Engineering, Dundigal, India. His research interests include Nanoelectronics, low power circuit design, carbon nano tubes, FinFET.

Sadulla Shaik (SM'13–M'17) received the B.Tech. degree in Electrical and Electronics Engineering from V.T.U., Belgaum, Karnataka, India, in 2003,

M.E, degree in Applied Electronics, from ANNA University Tamilnadu, India in 2005, and Ph.D, degree in VLSI, from Acharya Nagarjuna University Guntur, India in 2018. He is presently working as an Associate Professor in Vignan's Foundation for Science, Technology & Research University, Guntur, India. His research interests include Tunnel FETs with circuit co-design for ultra-low power/energy efficient circuit design.

**Pittala Chandra Shekar** (SM'13–M'17) received the B.Tech degree in electronics and communication engineering from Jawaharlal Nehru Technological University, Kakinada in 2009, M.Tech degree in VLSI design from Vignan's Foundation for Science, Technology & Research, Vadlamudi in 2011, Ph.D degree from Vignan's Foundation for Science, Technology & Research, Vadlamudi in 2017. He is presently working as an associate professor in the Department of Electronics & Communication Engineering at Institute of Aeronautical Engineering, Dundigal, India. His research interests include Nanoelectronics, low power circuit design, carbon nano tubes, FinFET.

**P. Manoja** received the B.Tech degree in electronics and communication engineering from Institute of Aeronautical Engineering, Dundigal, in 2018. She is currently working as Software Analyst, Syntizen technologies private limited, Hyderabad, India. Her research interests include low power digital circuits, nanoelectronics.

**R.** Abhinaya received the B.Tech degree in electronics and communication engineering from Institute of Aeronautical Engineering, Dundigal, in 2018. She is currently working as trading associate operations, IVY Comptech, Hyderabad, India. Her research interests include high speed biomedical circuits, FinFET applications.

**M. Rachana** received the B.Tech degree in electronics and communication engineering from Institute of Aeronautical Engineering, Dundigal, in 2018. She is currently working as software engineer, Capgemini, Hyderabad, India. Her research interests include energy harvesting, quantum mechanics.

**N. Nikhil** received the B.Tech degree in electronics and communication engineering from Institute of Aeronautical Engineering, Dundigal, in 2018. She is currently working as Capgemini, Hyderabad, India. His research interests include high speed low power digital/analog circuits, IoT.

# **Creative Commons Attribution License 4.0** (Attribution 4.0 International, CC BY 4.0)

This article is published under the terms of the Creative Commons Attribution License 4.0 https://creativecommons.org/licenses/by/4.0/deed.en\_US