# Analytical Drain-Current Model and Surface-Potential Calculation for Junctionless Cylindrical Surrounding-Gate MOSFETs

Billel Smaani<sup>1,2</sup>, Samir Labiod<sup>2,3</sup>, Fares Nafa<sup>4</sup>, Mohamed Salah Benlatreche<sup>5</sup>, Saida Latreche<sup>2</sup>

<sup>1</sup>Ingénierie des Systémes Electriques Department, Faculty of Technology, Boumerdes University, Algeria

<sup>2</sup>Laboratoire Hyperfréquences et Semiconducteurs, Electronique Department, Constantine 1 University, Algeria

<sup>3</sup>Physique Department, Faculty of Sciences, Skikda University, Algeria

<sup>4</sup>Boumerdes university, Faculté de Technologie, Laboratoire d'Ingénierie des Sytémes et des Telecommunication, Boumerdes, Algeria

<sup>5</sup>Centre Universitaire Abdel Hafid Boussouf Mila, Algeria

\*Corresponding author is Billel Smaani: b.smaani@univ-boumerdes.dz

Received: April 12, 2021. Revised: September 18, 2021. Accepted: September 8, 2021. Published: September 10, 2021.

Abstract—In this paper, we propose an analytical draincurrent model for long-channel junctionless (JL) cylindrical surrounding-gate MOSFET (SRG MOSFET). It is based on surface-potential solutions obtained from Poisson's equation using some approximations and separate conditions. Furthermore, analytical compact expressions of the drain-current have been derived for deep depletion, partial depletion, and accumulation mode. The confrontation of the model with TCAD simulation results, performed with Silvaco Software, proves the validity and the accuracy of the developed model.

Keywords—Cylindrical surrounding-gate (SRG) MOSFET, junctionless (JL), analytical drain-current model, surface-potential.

# I. INTRODUCTION

The junctionless transistors (JLTs) have attracted increasing attention from the scientific community and even the microelectronics industry since the development of these devices [1, 2]. The JLTs are depletion-mode devices with a highly doped channel and without junctions through the realization of one single type of doping concentration. Also, this type of transistors presents a near ideal subthreshold slope (~60mV/Dec), low leakage currents and less degradation of the mobility compared with the inversion mode transistors [3].

On the other hand, the cylindrical surrounding-gate MOSFET (SRG MOSFET) remains the best multiple-gate MOSFET transistor in terms of short channel effects (SCEs) control [4]. In addition, the junctionless (JL) SRG MOSFET transistor exhibits good electrical properties and excellent performances for future nanoscale CMOS circuits [5].

The electrostatic surface potential is an important parameter for describing DC property of junctionless devices. This key parameter is obtained from solving Poisson's equation using adequate boundary conditions. However, the difficulty of solving Poisson's equation in the cylindrical coordinates limits the development of analytical compact models for junctionless (JL) SRG MOSFET. Therefore, most of the developed analytical models for long-channel JL SRG MOSFET are "charge-based models" and a few of them are "surfacepotential based models" [6, 7]. The theory of JL Nanowire devices is well described in [8], however the using of the Bessel functions complicated the analytical formulation of the derived solutions. In [9], the current-model for JL Nanowire is continuous but there are no analytical expressions for the drain-current and it is based on direct integral operations. In [10], the quantum mechanical effect is well incorporated in the model but it is valid just for depletion regimes.

In this paper, we propose an analytical drain-current model for long-channel JL SRG MOSFET valid in all operating regions. It is based on the calculation of surface-potential obtained from relationships between surface potential and gate-voltage, which are derived from Poisson's equation using a regional

Volume 15, 2021

(4)

approach and separated considerations, this for each operating region: deep depletion, partial depletion and accumulation. The current expressions of the model have the advantages of being simple and compact, which makes the model appropriate for the accurate description of JL SRG MOSFET behavior and useful for developing compact models of long-channel triple-materials JL SRG MOSFET. In addition, the simplicity of the model facilitates the implementation in hardware description languages (HDL), which means that the proposed model is suitable for use in circuit simulators.

# II. FORMULATION OF THE MODEL EQUATION

### A. Electrostatic surface-potential

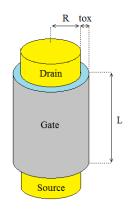

Let's consider the structure of JL SRG MOSFET shown in Fig. 1. Where *L* is the channel Silicon length,  $t_{ox}$  is the oxide thickness, *R* is the radius of cylindrical Silicon channel,  $V_{gs}$  is the gate bias, and  $V_{ds}$  is the drain bias [11].

Fig. 1 schematic view of 3-D junctionless (JL) SRG MOSFET

In the case of long-channel JL SRG MOSFET, the usual Poisson's equation can be written as [7]:

$$\frac{\partial^2 \Phi}{\partial r^2} + \frac{1}{r} \frac{\partial \Phi}{\partial r} = \frac{qN_d}{\varepsilon_{si}} \left[ \exp\left(\frac{\Phi(r) - V}{\Phi_t}\right) - 1 \right]$$

(1)

where  $\Phi$  is the electrostatic potential, *V* is the potential shift due to the electron quasi-Fermi level,  $N_d$  is the channel doping concentration,  $\varepsilon_{si}$  is the permittivity of Silicon,  $\Phi_t(=KT/q)$  is the thermal voltage, *q* is the charge of electron, *K* is the Boltzmann constant, *T* is the temperature and *r* is the radial coordinate.

The boundary conditions for Eq. (1) are:

$$\left. \frac{\partial \Phi}{\partial r} \right|_{r=R} = \frac{Q_{tot}}{\varepsilon_{si}} \tag{2}$$

$$\left. \frac{\partial \Phi}{\partial r} \right|_{r=0} = 0 \tag{3}$$

with  $Q_{tot}$  is the total charge densities per unit area in the channel.

Applying the Gauss theorem and using Eq. (2), we can

obtain:

$$C_{ox}(V_{gs} - V_{fb} - \Phi_S) = -\varepsilon_{si}E_S$$

where  $C_{ax} = \varepsilon_{ax}/R \ln(1 + t_{ax}/R)$  is the oxide capacitance11),  $V_{fb} = \Phi_{ms} + \Phi_t \ln(N_d/n_i)$  is the flat-band voltage,  $\Phi_s$  is the surface potential at the silicon–oxide interface and  $E_s$  is the surface electric field at the silicon–oxide interface.  $\varepsilon_{ax}$  is the permittivity of the oxide,  $\Phi_{ms}$  is the work-function difference between the metal gate and the channel and  $n_i$  is the intrinsic concentration.

Under depletion conditions, the right-hand side of Eq. (1) is equal to  $-qN_d/\varepsilon_{si}$  when  $R-r_d \le r \le R$ , with  $r_d$  is the depletion width. Then, after calculating the integral in Eq. (1), the electrostatic potential  $\Phi(r)$  can be written as [10]:

$$\Phi(r) = -\frac{qN_d}{4\varepsilon_{si}} \left( r^2 - \left( R - r_d \right)^2 \right) + \frac{qN_d}{2\varepsilon_{si}} \left( \left( R - r_d \right)^2 \ln \left( \frac{r}{R - r_d} \right) \right)$$

(5)

Replacing *r* with *R* and after some rearrangements, the surface potential  $\Phi_s$  can be expressed as:

$$\Phi_{S} = V - \frac{qN_d}{4\varepsilon_{si}} \left( 2(R - r_d)^2 \ln\left(\frac{R}{R - r_d}\right) - r_d(r_d - 2R) \right)$$

(6)

However, we can't compute the surface potential from Eq. (6) because of the undefined  $r_d$  parameter.

Using Eq. (6), Eq. (2), Eq. (4) and with some approximations, we get an important relation for the surface potential  $\Phi_s$  in fully depletion mode:

with  $V_{g_{as}} = V_{gs} - V_{fb}$  is the effective gate voltage,  $Q_{dep} = \pi q N_d R^2$  is the fixed charge density,  $\beta = C_{ox} / (4\pi \varepsilon_{si})$ , and  $\delta = Q_{dep} / 2\pi \varepsilon_{si}$ .

In partly depleted mode, the left-side hand of Eq. (7) can be

equal to

$$-\Phi_t \left[ \exp\left(\frac{\Phi_s - V}{\Phi_t}\right) - \left(\frac{\Phi_s - V}{\Phi_t}\right) - 1 \right] .8)$$

Moreover, in accumulation regime, the surface electric field  $E_s$  can be approximated by the following expression [12]:

$$E_{s} \approx -\sqrt{\frac{2qN_{d}\Phi_{t}}{\varepsilon_{si}}} \left[ \exp\left(\frac{\Phi_{s}-V}{\Phi_{t}}\right) - \left(\frac{\Phi_{s}-V}{\Phi_{t}}\right) - 1 \right]$$

(8)

Now, by substituting the solution of Eq (8) in Eq (4), we get:

$$V_{gs} - V_{fb} - \Phi_{S} = \frac{\varepsilon_{si}}{C_{ox}} \sqrt{\frac{2qN_{d}\Phi_{t}}{\varepsilon_{si}}} \left[ \exp\left(\frac{\Phi_{S} - V}{\Phi_{t}}\right) - \left(\frac{\Phi_{S} - V}{\Phi_{t}}\right) - 1 \right]$$

(9)

After some algebraic manipulations of Eq. (9) and neglecting the term  $(\Phi_s - V)/\Phi_t$ , the relation between the

surface potential  $\Phi_s$  and the voltages in the accumulation mode can be written as:

$$\Phi_{S}\left(\Phi_{S}-2V_{g_{ss}}\right)+V_{g_{ss}}^{2}=\eta\left(\exp\left(\frac{\Phi_{S}-V}{\Phi_{t}}\right)-1\right)$$

(10)

with  $\eta = (2qN_d\varepsilon_{si}\Phi_t)/C_{ox}^2$ .

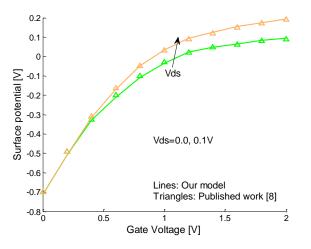

Fig. 2 presents the variation of surface-potential  $\Phi_s$  as a function of the gate-voltage  $V_{gs}$  for two different values of the drain-voltage  $V_{ds} = 0.0V$  and  $V_{ds} = 0.1V$ . In this case, we compare the obtained surface-potential with the results of the published work in [8]. It is clear that the agreement is good from deep-depletion to accumulation regime.

Fig. 2 electrostatic surface-potential versus gate-voltage, with  $t_{ox}$ =2nm, R=10nm and  $N_d$ =10<sup>19</sup>cm<sup>-3</sup>

#### B. Analytical drain-current

The drain-current  $I_{ds}$  can be obtained through the integral of the mobile charge density  $Q_{mob}$  from the source-side to the drain-side [13]:

$$I_{ds} = -2\pi \Phi_t \mu \frac{R}{L} \int_{V_c}^{V_c} Q_{mob}(V) dV$$

(11)

with  $\mu$  is the carrier mobility,  $V_s$  is equal to zero and  $V_d$  is equal to  $V_{ds}$ .

The total charge density in the channel  $Q_{tot}$  is the sum of the mobile charge density  $Q_{mob}$  and the fixed charge density  $Q_{dep}$ . Therefore, the mobile charge density in the channel  $Q_{mob}$  is equal to  $Q_{tot} - Q_{dep}$ . Based on the general definition of  $Q_{mob}$  and using Eq. (2) and Eq. (4), we get the following relation:

$$Q_{mob} = -C_{ox}(V_{g_{q}} - \Phi_S) - Q_{dep}$$

(12)

Substituting Eq. (12) in Eq. (11), we obtain:

$$I_{ds} = 2\pi \Phi_t \mu \frac{R}{L} \int_{V_1}^{V} \left[ C_{ox} (V_{g_{as}} - \Phi_S) + Q_{dep} \right] dV$$

(13)

From Eq. (7) we derive  $dV/d\Phi_s$  as follows:

$$\frac{dV}{d\Phi_{s}} = 1 + 2\beta \left( \ln(R) - \frac{1}{2} \ln\left(R^{2} \left(1 + \frac{2}{\delta}\beta \left(V_{g_{s}} - \Phi_{s}\right)\right)\right) \right)$$

(14)

Integrating Eq. (13) using Eq. (14), we obtain the expression of the drain-current  $I_{ds}$  in fully depleted mode, as such as:

$$I_{ds} = 2\pi \Phi_t \mu \frac{R}{L} \Biggl\{ C_{ox} \left[ i_c^p - \left( \frac{1}{2} + \left( \frac{1}{4} + \ln(R) \right) \beta \right) V_{g_{eff}}^2 + \frac{1}{4} \delta V_{g_{eff}} + \left( \frac{3}{4} + \ln(R) + \frac{1}{2\beta} \right) \frac{\delta^2}{4\beta} \Biggr] + Q_{dep} V \Biggr\}_S^D$$

(15)

with,

$$\begin{split} i_c^p &= \left( \left( \frac{\Phi_s}{2} - V_{g_{s_s}} \right) \Phi_s + \frac{V_{g_{s_s}}^2}{2} - \frac{\delta^2}{8\beta^2} \right) \\ &\times \beta \ln \left( \frac{R^2}{\delta} \left( \left( V_{g_{s_s}} - \Phi_s \right) 2\beta + \delta \right) \right) \\ &- \left( \left( \frac{1}{4} + \ln(R) \right) \beta + \frac{1}{2} \right) \Phi_s^2 + \left( \left( 1 + \left( \frac{1}{2} + 2\ln(R) \right) \beta \right) V_{g_{s_s}} - \frac{\delta}{4} \right) \Phi_s \end{split}$$

where D and S denotes, receptively,  $\Phi_s(L)$  and  $\Phi_s(0)$ .

For partly depleted mode, we derive  $dV/d\Phi_s$  based on the general solution of Eq. (7), as:

$$\frac{dV}{d\Phi_{s}} = 1 - \exp\left(\frac{\Phi_{s} - V}{\Phi_{t}}\right) + 2\beta\left(\ln(R) - \frac{1}{2}\ln\left(R^{2}\left(1 + \frac{2}{\delta}\beta\left(V_{g_{s}} - \Phi_{s}\right)\right)\right)\right)$$

(16)

the solution of Eq. (16) is obtained from Eq. (7) with the leftside hand equal to  $-\Phi_t \left[ \exp\left(\frac{\Phi_s - V}{\Phi_t}\right) - \left(\frac{\Phi_s - V}{\Phi_t}\right) - 1 \right].$

Furthermore, the integration of Eq. (13) with the using of Eq. (16) allow us to get the expression of the drain-current in partly depleted mode as:

$$I_{ds} = 2\pi \Phi_t \mu \frac{R}{L} \left\{ C_{os} \left[ \left( \Phi_s - V_{g_{ss}} - \Phi_t \right) \Phi_t \exp\left( \frac{\Phi_s - V}{\Phi_t} \right) + i_c^p + \left( \delta - \beta V_{g_{ss}} \right) \frac{V_{g_{ss}}}{4} + \frac{3\delta^2}{16\beta} \right] + Q_{dep} V \right\}_R^D$$

(17)

It is noting that  $i_c^p$  is a part of the current which is a common factor between the expression of the current in fully depleted mode and the expression of the current in partly depleted current.

To ensure a continuous solution of the current for the two depletion regimes, we use an interpolation function based on the square root of the algebraic sum between Eq. (15) and Eq. (17) [14].

In the case of accumulation mode, the term  $dV/d\Phi_s$  is

obtained from Eq. (10), as:

$$\frac{dV}{d\Phi_{s}} = 1 - \frac{2\Phi_{t}(\Phi_{s} - V_{g_{s}})}{\Phi_{s}(\Phi_{s} - 2V_{g_{s}}) + V_{g_{s}}^{2} + \eta}$$

(18)

Also, the expression of the drain-current in accumulation mode is obtained as follows:

$$I_{ds} = 2\pi \Phi_t \mu \frac{R}{L} \left\{ C_{ox} \left[ \left( V_{g_{ox}} + 2\Phi_t \right) \Phi_s - \frac{\Phi_t^2}{2} - 2\Phi_t \sqrt{\eta} \arctan\left( \frac{\Phi_s - V_{g_{oy}}}{\sqrt{\eta}} \right) \right] + Q_{dep} V \right\}_s^D$$

(19)

#### III. RESULTS AND DISCUSSION

To validate the proposed model, we performed the 3-D numerical simulation of JL SRG MOSFET using Atlas tool of Silvaco-TCAD [15]. In this case, we have considered a longchannel N<sup>+</sup>/N<sup>+</sup>/N<sup>+</sup> junctionless (JL) SRG MOSFET with 10 nm lengths of the Source/Drain regions and 5.2eV for the gate workfunction. In addition, we have considered the driftdiffusion model with a constant mobility of 100cm<sup>2</sup>/Vs [7, 16]. Then, the drain-current  $I_{ds}$  is extracted and plotted for different gate-voltage  $V_{gs}$  and drain-voltage  $V_{ds}$ . Also, with varying the device geometrical parameters such as the oxide thickness  $t_{ox}$  and the channel radius R. This, for a good confrontation of the model results with the obtained numerical simulations results.

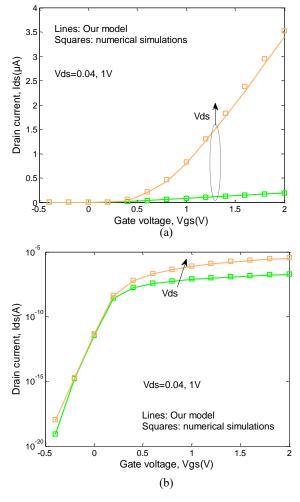

Fig. 3 shows the variation of the drain-current  $I_{ds}$  as a function of the gate-voltage  $V_{gs}$  for low and high values of the drain-voltage ( $V_{ds} = 0.04V$  and  $V_{ds} = 1V$ ). We compare the modeled drain-current with the numerical simulations results in linear scale (Fig. 3(a)) and semi-logarithmic scale (Fig. 3(b)). It indicates that our model (in lines) reproduce the good behavior of the current in deep-depletion, partial depletion and accumulation mode. Also, the good accuracy of the model is observed trough the device simulations results (in squares).

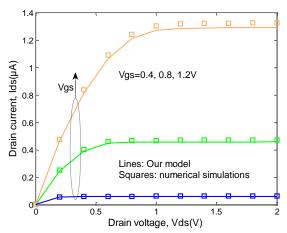

The variation of the drain-current  $I_{ds}$  versus the drainvoltage  $V_{ds}$  is well presented in Fig. 4. With the increase of the gate-voltage ( $V_{gs} = 0.4, 0.8, 1.2V$ ), the variation of the modeled drain-current (in lines) is in good agreement with the results of numerical simulations (in squares). A slight difference is observed between the results of the model and the numerical simulations results in accumulation regime, it is related to the strong values of the gate voltage  $V_{gs}$  with the drain voltage  $V_{ds}$ . However, the accuracy is acceptable and the agreement remains good.

Fig. 3 transfer characteristic in (a) linear scale and (b) semilogarithmic scale,  $L=1 \mu m$ ,  $t_{ox} = 5 nm$ , R=5 nm and  $N_d=10^{19} cm^{-3}$

Fig. 4 output characteristic with varying the gate-voltage Vgs=0.4, 0.8, 1.2V,  $L=1\mu$ m,  $t_{ox}=5$ nm, R=5nm and  $N_d=10^{19}$ cm<sup>-3</sup>

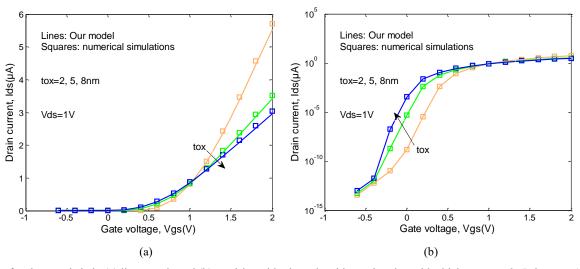

Fig. 5 shows the variation of the drain-current  $I_{ds}$  against the gate-voltage  $V_{gs}$  with different values of the oxide thickness  $t_{ox} = 2, 5, 8nm$ . In this case, the variation of the current is plotted in linear scale (Fig. 5(a)) and semi-logarithmic scale (Fig. 5(b)). It can be clearly seen that the current  $I_{ds}$  is increasing with the increase of  $t_{ox}$  in depletion mode, but in the accumulation regime, the current  $I_{ds}$  is decreasing with the increase of  $t_{ox}$ . Also, an intersection point between  $I_{ds}(V_{gs})$  curves is observed when the gate-voltage  $V_{gs}$  is equal to the flat-band voltage  $V_{fb}$  (~1.1V) [17].

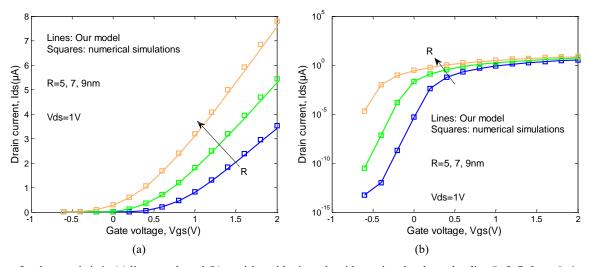

Fig. 6 illustrates the influence of varying the channel radius R on the transfer characteristics of JL SRG MOSFET obtained with the proposed model. The curves are plotted in linear scale (Fig. 6(a)) and semi-logarithmic scale (Fig. 6(b)).

It should be pointed that the drain-current is strongly increased with the increase of the technological parameter R.

The present model reproduces well the dependence of JL SRG MOSFET with the geometrical parameters such as the channel radius R and the oxide thickness  $t_{ox}$ . It is found that, the dependence of the current  $I_{ds}$  with R parameter is more important comparing with  $t_{ox}$  parameter. In addition, the result of the proposed model (in lines) matches well with the numerical simulations results (in squares).

Fig. 5 transfer characteristic in (a) linear scale and (b) semi-logarithmic scale with varying the oxide thickness  $t_{ox}=2, 5, 8$  nm,  $L=1\mu$ m, R=5 nm and  $N_d=10^{19}$  cm<sup>-3</sup>

Fig. 6 transfer characteristic in (a) linear scale and (b) semi-logarithmic scale with varying the channel radius R=5, 7, 9nm,  $L=1\mu$ m,  $t_{ox}=5$ nm and  $N_d=10^{19}$  cm<sup>-3</sup>

# IV. CONCLUSIONS

We have developed an analytical drain-current model based on the surface-potential calculation for JL SRG MOSFET. It is a physical-based model in which the expressions of the draincurrent are expressed in terms of surface potentials obtained from Poisson's equation. Then, we have validated the proposed model in all regimes of operations using the 3-D numerical simulations results of JL SRG MOSFET obtained with Silvaco Software. In this case, we have found that the proposed model is in good agreement with the numerical simulations results. In addition, the analytical expressions of the drain-current are simple, compact and have no fitting parameters. On the other hand, the considered approach gives an accurate description of the JL SRG MOSFET behavior. Moreover, the present work is very helpful for developing analytical compact models of long-channel triple-materials JL SRG MOSFET and also for the integration of short channel effects (SCEs).

# REFERENCES

- C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J.-P. Colinge, "Junctionless multigate field-effect transistor," Appl. Phys. Lett., vol. 94, no. 5, pp. 053511-1–053511-2, 2009.

- [2] C.-W.Lee, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti Akhavan, P. Razavi, and J.-P. Colinge, "Performance estimation of junctionless multigate transistors," Solid-State Electronics, 54, pp. 97–103, 2010.

- [3] J.-P. Colinge et al., "Nanowire transistors without junctions," Nature Nanotechnol., vol. 5, no. 3, pp. 225– 229, 2010.

- [4] F. A. Noor, C. Bimo, I. Syuhada, T. Winata, and K. Khairurrijal, "A compact model for gate tunneling currents in undoped cylindrical surrounding-gate metaloxide-semiconductor field-effect transistors," Microelectronic Engineering, 216, 111086, 2019.

- [5] A. Nazarov, J-P. Colinge, F. Balestra, J-P. Raskin, F. Gamiz, and V. Lysenko, Semiconductor-On-Insulator Materials for Nanoelectronics Applications, Springer, 2011.

- [6] J. P. Duarte, S.-J. Choi, D.-I. Moon, and Y.-K. Choi, "A nonpiecewise model for long-channel junctionless cylindrical nanowire FETs," IEEE Electron Device Lett., vol. 33, no. 2, pp. 155–157, 2012.

- [7] F. Lime, O. Moldovan, and B. Iñiguez, "A Compact Explicit Model for Long-Channel Gate-All-Around Junctionless MOSFETs. Part I: DC Characteristics," IEEE Transactions on Electron Devices, vol. 61, no. 9, pp. 3036–3041, 2014.

- [8] E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, "Theory of the junctionless nanowire FET," IEEE Trans. Electron Devices, vol. 58, no. 9, pp. 2903–2910, Sep. 2011.

- [9] J. X.-Shi, L. Xi, K. H.-In, and L. J.-Ho, "A Continuous Current Model of Accumulation Mode (Junctionless) Cylindrical Surrounding-Gate Nanowire MOSFETs," Chin Phys Lett, vol. 30, no. 3, pp. 038502-1 – 038502-4, 2013.

- [10] B. Sorée, W. Magnus, and G. Pourtois, "Analytical and self-consistent quantum-mechanical model for a surrounding gate MOS nanowire operated in JFET mode," J. Comput. Electron., vol. 7, no. 3, pp. 380–383, 2008.

- [11]B. Smaani, S. Latreche, and B. Iniguez, "Compact draincurrent model for undoped cylindrical surrounding-gate metal-oxide semiconductor field effect transistors including short channel effects," J. Appl. Phys., vol. 114, pp. 224507-1–224507-6, 2013.

- [12] J.-P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, R. Yu, A. N. Nazarov, and R. T. Doriac,

"Reduced electric field in junctionless transistors," Appl. Phys. Lett., vol. 96, no. 7, pp. 073510-1–073510-3, 2010.

- [13]N. Arora, 'MOSFET Modeling for VLSI Circuit Simulation: Theory and Practice'', World Scientific, 2011.

- [14] Z. Chen, Y. Xiao, M. Tang, Y. Xiong, J. Huang, J. Li, X. Gu, and Y. Zhou, "Surface-Potential-Based Drain Current Model for Long-Channel Junctionless Double-Gate MOSFETs," IEEE Transactions on Electron Devices, vol. 59, no. 12, pp. 3292 – 3298, 2012.

- [15] Device simulator ATLAS, Silvaco International, 2007.

- [16] O. Moldovan, F. Lime, S. Barraud, B. Smaani, S. Latreche and B. Iñiguez, "Experimentally verified draincurrent modelfor variable barrier transistor," Electronics letters, vol. 51, no. 17, pp. 1364 – 1366, 2015.

- [17] B. Smaani, Y. Yakhelef, F. Nafa, M. S. Benlatreche and S. Latreche, "Analysis of the Gate-To-Channel Capacitance Variation for the Tri-Gate Nanowire Junctionless Transistors," 2021 Global Conference on Engineering Research (GLOBCER'21), pp. 54-60, 02 Jun- 05 Jun 2021.

# Contribution of Individual Authors to the Creation of a Scientific Article (Ghostwriting Policy)

Billel Smaani carried out the analytical model development.

Samir Labiod has implemented the developed model in Matlab.

Fares Nafa has improved the English of the article.

Mohamed Salah Benlatreche carried out the TCAD simulation of the transistor.

Saida Latreche was responsible for the optimisation of the developed model and also the article.

# Creative Commons Attribution License 4.0 (Attribution 4.0 International, CC BY 4.0)

This article is published under the terms of the Creative Commons Attribution License 4.0

https://creativecommons.org/licenses/by/4.0/deed.en US