# FPGA Realization of Open/Short Test on IC

W.L. Pang, K. W. Chew, Florence Choong, C.L. Tan

4. Serve as the pioneer to design other type of IC testing tester as the sing the FPGA

Abstract— IC (Integrated Circuitry) testing requires the sing the FPGA very advanced and sophisticated Advance Test Equipment (ATE) that costs multi million USD. The cost of IC testing is increasing yearly and it will exceed the cost of manufacturing in future. The manufacturers are interested to lower down the manufacturing cost. Low cost tester is one of the options to reduce the manufacturing cost. The low cost FPGA realization of Open/Short Test on IC is introduced to reduce the IC test cost. The open short test is selected, because it is the first IC test. The Very High Speed Integrated Circuit Hardware Description Language (VHDL) is used to model the Open/Short Test on IC and the design is capable to perform the open/short test.

Keywords -- IC tester, open short test, VHDL modeling

# I. INTRODUCTION

HE cost of an integrated circuit (IC) includes the design cost, The manufacturing cost and the testing cost. The IC testing becomes more challenging and complex when the IC become smaller and more transistors accommodated in a single IC. A very advance and sophisticated ATE that costs multi million USD is required to perform the IC testing. The manufacturers always try to reduce the manufacturing costs to control the IC selling price.

The low cost FPGA realization of open/short tester approach can reduce the manufacturing costs. The FPGA is a programmable logic device (PLD) that can be programmed to perform any digital tasks. The implementation cost of the FPGA is low because the FPGA is reprogrammable and has very high density of logics available for programming and also acts as storage elements.

A prototype of FPGA open/short tester is designed. The prototype tester can measure 4 IC pins only to perform the open short test, because the same method can be duplicated to support more test pins. It can be easily duplicated to measure 8 IC pins, 16 IC pins or even 100 IC pins by increasing the number of hardware designed. The FPGA open/short tester is more cost effective compare to the Agilent technologies and Tektronix testers.

The objectives of the project are:

- 1. Design and realize the open/short test on IC tester that is capable to perform open/short test on 4 IC pins using the FPGA with the aid of other external hardware

- The designed open/short test on IC tester using the FPGA must be able to perform the open/short test on IC correctly

- 3. The developed open/short test on IC tester must be cost effective

Manuscript received Febr. 4, 2007: Revised version received July 14, 2007. All Authors are with the Multimedia University, 63100 Cyberjaya, Selangor, Malaysia (phone: 603-83125376; e-mail: ericpang27@yahoo.com).

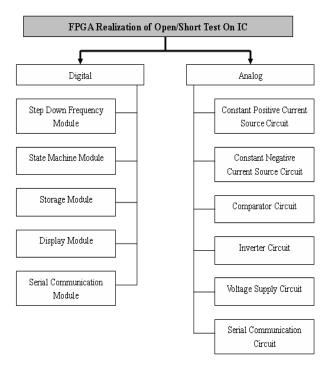

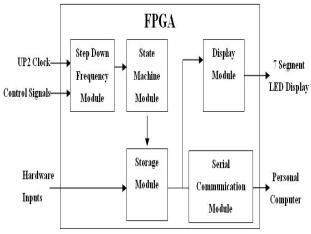

This project is divided into 2 major parts as shown in Fig 1, the digital part and analog part. The digital part is to design and configure the digital blocks designed into the FPGA chip using the VHDL. The analog part is to design the hardware that is able to perform the open/short test on IC and interface well with the FPGA at the digital part.

Fig 1: Project scopes

## II. ESD TEST

The IC fabrications are dominated by the advanced Complementary Metal Oxide Semiconductor (CMOS) technology because the CMOS IC will have low static power consumption, high noise margin and high integration. However the MOS devices are particularly vulnerable to ESD event [1]. The ESD phenomena become a serious problem for fabricated by deep-submicron CMOS products technologies. Electrostatic discharge (ESD) refers to the sudden transfer (discharge) of static charge between objects at different electrostatic potential [2]. It belongs to the family of electrical problems known as electrical overstress (EOS). Other members of EOS family include lighting and electromagnetic pulses (EMP). ESD/EOS is responsible for nearly 40% of the failed integrated circuits (ICs) returned by customer [1].

The three primary ESD test methods are HBM (Human Body Model), MM (Machine Model) and CDM (Charge

Issue 2, Vol. 1, 2007

Device Model). The models used to perform device testing cannot duplicate the full spectrum of all possible ESD events. But these models have been proven to be successful in reproducing over 95% of all ESD field failure signatures [3].

Since the ESD brings serious problems to the electronics industry, a numbers of methods have been implemented in order to counter or solve the ESD on the electronic devices. By knowing prevention is better than cure, prevention on the ESD is a must and fundamental in order to produce high reliable and high performances ICs and electronics devices. Several techniques have been used in order to avoid the ESD on the electronic devices. Some of the techniques used in preventing the ESD are charge prevention, shielding, grounding, neutralization and education.

For example, in the workstation, it is essential to handle all handle ESDS devices at static-safe workstations. It is very important to avoid bringing sources of static electricity within 1m near the static-safe workbench. Use the special model of air-gun which will not generate electrostatic charge in the air stream. Make sure all the machines or equipment have a common ground point. Shield against the electrostatic sources or electrostatic victims so that no charge transfer between the materials or equipments. This is done using the *Faraday Cage* concept. Metallized shielding bags are commonly used to protect static sensitive electronic components and assemblies by creating a Faraday Cage effect. Keep the humidity inside the workstation at 40% or higher because hot and dry conditions can cause ESD.

# III. I-V CHARACTERISTIC OF DIODE

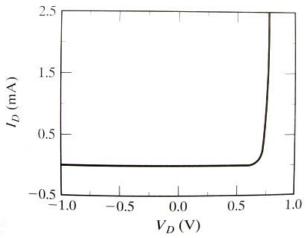

As 0 bias voltage applied to the pn junction, there is no forward current as shown in Fig 2. As the bias voltage applied gradually increased, the forward current and the voltage across the pn junction gradually increased. When the forward bias voltage applied increase approximate to 0.7V, the forward current will increase rapidly. As the forward bias voltage continue to increase, the current will continue to increase quickly but the voltage across the pn junction will only experience very little increment.

Fig 2: I-V Characteristic of Diode under Forward Bias Condition

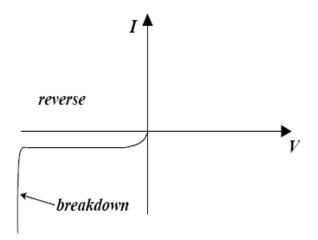

Increase the reverse voltage applied across the pn junction will result on the voltage across the pn junction increase linearly, but only extreme small amount of reverse current, I flow through the pn junction. When the reverse voltage  $V_R$  reaches its breakdown value,  $V_{BR}$ , the reverse current will begin to increase dramatically. The dramatic increase of the reverse bias current is caused by avalanche breakdown. The increase of the reverse bias voltage heightens the magnitude of the electrical field across the junction [5].

At a critical field  $E_{\rm crit}$ , the minority carriers at the space-charge region gain sufficient high energy level that electron-hole pairs are generated through the collision with immobile silicon atoms. These generated electron-hole pairs will further collide with other atom, to generate further addition electron-hole pairs, thus, the avalanche process. The avalanche breakdown is non-destructive process and its effect would be disappeared when the reverse bias voltage is removed. However it is not encourage keeping the diode operate at the avalanche breakdown mode as the high reverse current will lead to high power dissipation and it might permanently destroy the diode.

Fig 3: I-V Characteristic of Diode under Reverse Bias Condition

### IV. OPEN SHORT TEST

A diode will be in forward bias mode when apply a bias voltage greater than  $\sim 0.65 \, \text{V}$ , this is the threshold voltage of a normal voltage where a diode will be turned ON. When the diode turned on, it will act as a short circuit component to allow current flow through it with approximately  $0.65 \, \text{V}$  voltage drop across the diode. When apply a negative bias voltage onto the diode, the diode will act like an open circuit to deny or block the current flow through it. Though, in practical there is a very small amount of current called reverse saturation current, Saturation current flow through the diode under the reverse bias condition.

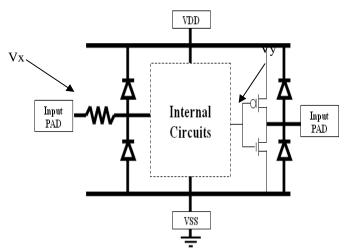

The PN junction diodes are used as the ESD clamp device. The ESD clamp device is shown in Fig 4. The bonding pad is used to connect the internal circuits of an IC to the outside world and between the bonding pad and Input/Output (I/O)

pins, there will be electrostatic discharge (ESD) clamp circuit to protect the IC from the ESD event. The simple ESD clamp circuit consists of a pair diodes connect in series as shown on Fig 4. Open/short circuit test on IC is performed by determine the whether both diodes which connected in series are function correctly or not. The diodes pair is used to perform the open short test.

Under normal condition, the voltage at point  $V_X$  will be greater than  $V_{SS}$  hence force the diode Dn1 into reverse bias mode. Same goes to diode Dp1; it will be reverse biased as the  $V_{DD}$  is greater than  $V_X$ . The ESD event can be model as applying an ESD voltage,  $V_{ESD+}$  at the input side. When a positive ESD voltage,  $V_{ESD+}$  is applied to the input pad, it makes voltage at point  $V_X$  greater than  $V_{DD}$ , hence force the Dp1 into forward bias condition. When the Dp1 is turned ON, all ESD current, IESD will be flow through the Dp1 into  $V_{DD}$ . The characteristic of the diode is when it is forward bias mode; the voltage dropped across it will be ~0.65-0.8V. By this characteristic, the high positive ESD voltage will be clamped from a few kilo volts down to approximately ~0.65 – 0.8 V.

When a negative ESD voltage apply to the output pad, it cause the voltage at point  $V_{\rm Y}$  is less than  $V_{\rm SS}$  hence force the diode connected to the  $V_{\rm SS}$  in reverse break down condition and diode connected to  $V_{\rm DD}$  in reverse bias. The ESD current will be flow from the  $V_{\rm SS}$  to the output pad through the diode, hence no ESD current flow into the internal circuits. From the study of the diode working in reverse break down mode, it acts like a short circuit but with voltage drop across the diode equal to the reverse bias voltage of the particular diode. The reverse bias voltage value can be designed by planning the layout the length, width and amount of impurities in the diode during the layout of the circuit. Hence, the high negative ESD voltage,  $V_{\rm ESD}$  can be clamped down significantly.

Fig 4: The diodes serve as the ESD clamp device

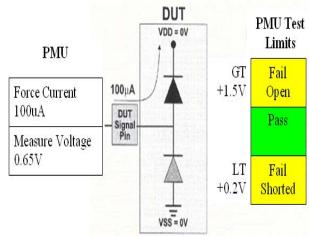

A precision measurement unit (PMU) is used to perform the open/short test. The PMU is the DC measurement devices. It clamps the voltage and current into a specific limited range of voltage and current. It also can set the upper and lower limit of the measure value to determine whether the device under test (DUT) is pass or fail the open/short test. It will forces the

current and measures the voltage or vice versa. The following steps are used to test the upper ESD diode:

- Ground all the pins including  $V_{SS}$  and  $V_{DD}$

- The PMU is used to force a positive current of  $\sim 100 \mu A$  to one IC pin at a time.

- The PMU clamps the voltage at +5.0V.

- The upper PMU test limit is set to fail the open test if the measured result is >1.5V.

- The lower PMU test limit is set to fail the short test if the measured result is <0.2V.

Fig 5 shows the configuration to measure the upper ESD diode.

Fig 5: PMU pump 100uA into the I/O pin and measure the voltage drop across the upper diode.

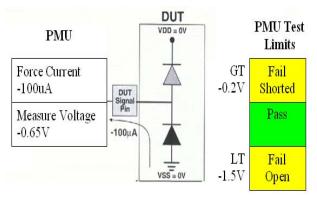

The following steps are used to test the lower ESD diode:

- Ground all pins including  $V_{SS}$  and  $V_{DD}$

- The PMU is used to force a negative current of  $\sim$  -100 $\mu$ A to one IC pin at a time.

- The PMU clamps the voltage at -5.0V.

- The upper PMU test limit is set to fail the short test if the measured result is > -0.2V.

- The lower PMU test limit is set to fail the open test if the measured result is < -1.5V.

Fig 6 shows the configuration to test the lower ESD diode.

The PMU is clamped the voltage at 5V in order to test the upper diode. The upper diode will be in forward bias and the lower diode will be in reverse bias because the  $V_{\rm DD}$  now is grounded (0V). The 100uA current will flow through the good upper diode and give a voltage drop about 0.4-0.7V across the upper diode.

Fig 6: PMU pump -100uA into the I/O pin and measure the voltage drop across the lower diode

The voltage measured is greater than 1.5V, if the pin is open circuit. This may caused by malfunction diode or the broken wire between the IC package and the die. No current will flow through the diode and the measured voltage will be floating  $\sim$  5V.

The voltage measured is less than 0.2V, if the pin fails the short test. The short circuit may cause by the test pin falsely in touch with other I/O pins which already ground in the first place. The current will flows to the ground that has lower resistance instead of the diode that has higher resistance.

Same theory is applied in test for lower diode, where everything will happen in the reverse way as all the supplied input voltage and output are in negative polarity.

## V.FIELD PROGRAMMABLE GATE ARRAY

The field programmable gate array (FPGA) has the similar architecture as general Complex Programmable Logic Device (CPLD). The main different between a FPGA and a CPLD is the different functional logic that used in their design. In the CPLD, the functional logic is called PLD but the functional logic in FPGA is called complex logic block (CLB). The density and size of a CLB is much smaller compare to size and density of a PLD. But inside a FPGA, there is much more CLBs compare to the numbers of PLDs inside the CPLD. These CLBs are distributed across the entire chip and connected through the programmable interconnection.

The UP2 Education Board is used for the FPGA realization. The UP2 Education Board is a stand-alone experiment board based on an Altera FLEX® 10K device and includes a MAX® 7000 device. The FLEX® 10K device is actually categorized as the Field Programmable Logic Array (FPGA) family. On the other hand the MAX® 7000 domican be categorized as Complex Programmable Logic D (CPLD) family.

## VI. VHDL

VHDL is a programming language that describes a d logic block by function, data flow behavior, and/or structhis hardware description language (HDL) is used to r

the behavior or function of the designed digital logic block and then only configure the PLD, such as FPGA or CPLD.

#### VII. DESIGN METHODOLOGY

The design of the FPGA Realization of Open/Short Test on IC is separated into a several digital blocks as shown on Fig 7. There are five main modules, step down frequency module, state machine module, storage module, display module and PC interface module.

Fig 7: Digital Blocks of FPGA Realization of Open/Short Test on IC

A step down frequency module is required to provide a clock signal that synchronises both the FPGA chip and the hardware circuitries. In Altera UP2 Education Board, a 25.175 MHz crystal oscillator is attached. However the hardware designed properly working at lower frequency than 25.175MHz. The step down frequency module step downs the frequency to the lower frequency. The frequency divide-by-N ( $f\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash\slash$

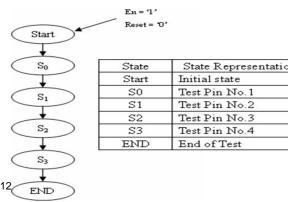

A finite state machine (FSM) is designed and is implemented using the VHDL. The FSM is used to automate a test sequence to perform the open/short test on Integrated Circuit (IC). The Moore machine is implemented as FSM, since the output of each state is fixed. The FSM is shown in Fig 8.

Fig 8: State Diagram and State Representation of the Designed Moore Machine

The FSM module controls the sequence of the IC pin that performing the open/short test. The result of the open/short tests on each individual IC pin are fetched into the FPGA to determine weather the IC pin pass or fail the open/short test. The data storage modules are used to store the open/short test results on each individual IC pin tested. The open/short test result carries two bits of binary information. An 8-bits register is required to store the result of the 4 pin IC open/short test and the result of the test is displayed using the dual-digit 7-segment displays attached at the UP2.

## VIII.SIMULATION RESULTS

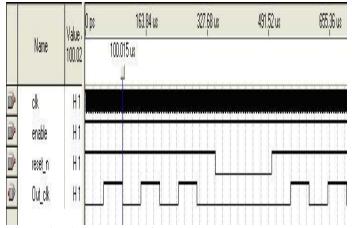

The step down frequency module is designed using the VHDL by setting the counter value, N = 1258. The specifications of the step down frequency module are:

$f_1 = f_0 (1/2N)$

Input frequency,  $f_0 = 25.175MHz$

Output frequency,  $f_1 = 10KHz$

The simulation result is shown in Fig 9. The output clock time period is 100.015us that is more than 100us that expected. The reason behind this is due the delay of logics required in construct the step down frequency module.

Fig 9: Simulation Result of the Step Down Frequency Module

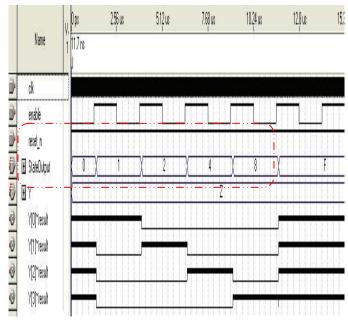

The state machine specifications are on Table 1 and the simulation result is shown in Fig 10. As shown in Fig 10, the "StateOutput" changed from START  $\rightarrow$  S0  $\rightarrow$  S1  $\rightarrow$  S2  $\rightarrow$  S3  $\rightarrow$ END as per design specifications required. The "Y" node is the IC pin that selected to perform the open/short test. The "Z000", represent the first IC pin is selected to perform open/short test on IC and other 3 IC pins are shorted. While the "Y" output is "0Z00", it represent the second IC pin is

selected to undergo the open/short test and the rest of 3 IC pins are shorted.

Table 1: StateOutput and Y Value

| State | State Output Value | Y Value |

|-------|--------------------|---------|

| Start | 0000               | ZZZZ    |

| S0    | 0001               | Z000    |

| S1    | 0010               | 0Z00    |

| S2    | 0100               | 00Z0    |

| S3    | 1000               | 000Z    |

| End   | 1111               | ZZZZ    |

Fig 10: Simulation Result of the State Machine Module

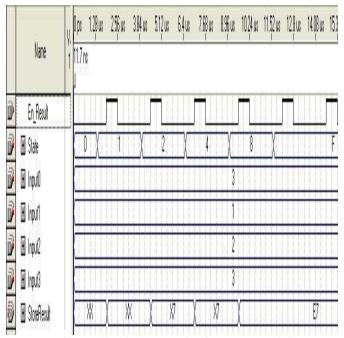

Fig 11 shows the simulation result of the storage module designed. The input ports are Input0, Input1, Input2 and Input3 and the 8-bits storage register is "StoreResult". With Input0="11", Input1="01", Input2="10" and Input3="11", the expected result of 8-bits register is "11100111" or "E7"in hexadecimal.

Fig 11: Simulation Result of Storage Module

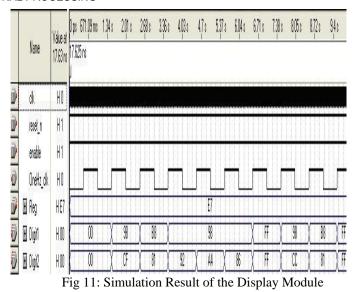

The dual 7-segment display output values are shown in Table 2 and the simulation result is shown in Fig 12. At the first positive edge, the state is START, and the output for the Digit1 and Digit2 of the dual-digit 7-segment displays are "00" and "00". At the second positive edge, the state is P1, where it means test the IC pin number one, the Digit1 and Digit2 will show alphabet "P" and "1" and its corresponding value is "98" and "CF". The third positive edge, the state change to "RP1" where it shows the open/short test result of IC pin one. For this case, the IC pin number one fails the open test. Digit1 and Digit2 will show alphabet "F" and "S" and the corresponding value is "B8" and "81".

Table 2: The Dual-Digit 7-Segment Output Value

| STATE      | Digit1 Value  | Digit2 Value  |

|------------|---------------|---------------|

|            | (Hexadecimal) | (Hexadecimal) |

| START      | 00            | 00            |

| P1         | 98            | CF            |

| P2         | 98            | 92            |

| P3         | 98            | 86            |

| P4         | 98            | CC            |

| Fail Short | В8            | A4            |

| Fail Open  | В8            | 81            |

| Pass       | 98            | A4            |

| Undefined  | В8            | В8            |

| END        | FF            | FF            |

Master Time Bar: 0 ps Pointer 2.96 us 2.96 us End 2.75 us 5.31 us 7.87 us 12.99 us 15.55 us 20.67 us 90.0 ns 10.43 us 18.11 us 23.23 us +12.905 us +2.735 us +7.82 us +17.99 us +23.075 us ck **∃** Digit1 ■ Digit2 enable1 enable2 Input0 ∄ Input1 ■ Input2 ■ Input3 reset\_n Y store\_valu Y[1]"resul Y[2]\*result

Fig 13: Simulation Result of Open/Short Test

tpin2 tpin3

The time required to perform open/short test on 4 upper protecting diodes are shown in Fig 13. The time required to perform open/short test on 4 upper protecting diodes are  $T_{upper} = t_{setup} + Nt_{pin}$ . The  $T_{setup}$  is the setup time of the open/short tester, N is the number of the IC pins tested and Tpin is the time required to perform the test on an upper protecting diode. The setup time,  $t_{setup}$  is 2.735us and  $t_{pin} = t_{pin1} - t_{pin2} = 5.085$ us. For N = 4, the  $T_{upper} = 23.075$ us. The time required performing the open/short test on the lower protecting diode, T<sub>lower</sub> is equal to the time required to perform open/short test on upper protecting diode. The total time,  $T_{tot}$  required to perform the open/short test on both the upper and lower protecting diode is  $T_{tot} = T_{lower} + T_{upper} + T_{delay} = 3.04615 \text{ms}$ . The  $T_{delay}$ , 3ms is required to turn on the negative voltage supply using a mechanical relay.

Y[3]\*result

tpin1

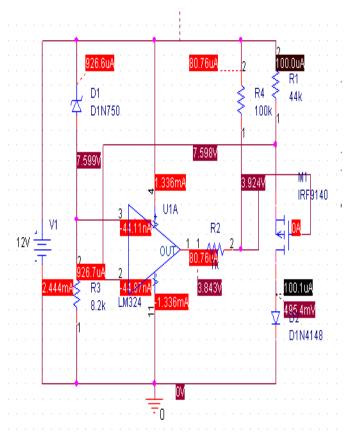

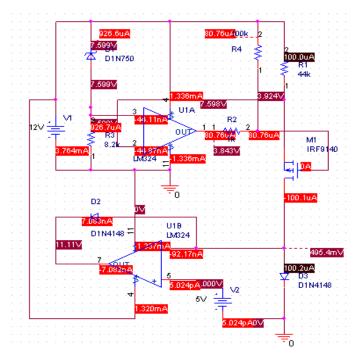

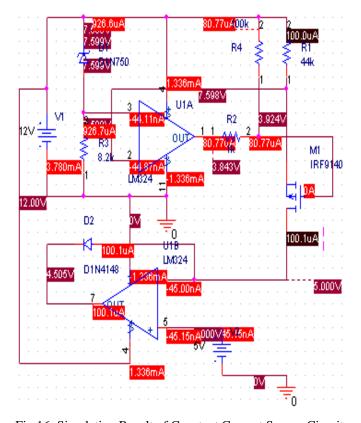

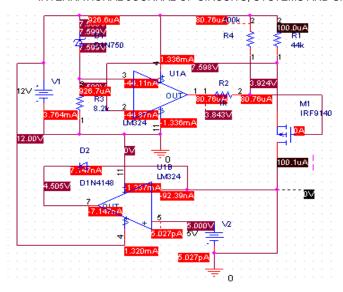

#### IX. CONSTANT POSITIVE CURRENT SOURCE CIRCUIT

The zener diode, D1N750 is used to provide the reference voltage,  $V_{\it REF}=4.4V$  V. In order to get a constant positive current at output,  $I_{\it OUT}=100uA$ .

The Fig 14 shows the schematic of constant positive current source circuit designed with the diode as a load. Fig 15, Fig 16 and Fig 17 show the simulation result of the constant positive current source with output varies from  $1k\Omega$  to  $100k\Omega$  .

Fig 14: Simulation Result of the Constant Positive Current Source Circuit with Diode, D1N4148 as Load

Fig 15: Simulation Result of Constant Current Source Circuit with Clamped Output Voltage to 5V with Load Diode, D3 Forward Biased

Fig 16: Simulation Result of Constant Current Source Circuit with Clamped Output Voltage to 5V with Load Open Circuited

Fig 17: Simulation Result of Constant Current Source Circuit with Clamped Output Voltage to 5V with Load Short Circuited

#### X.CONCLUSION

The open/short test design is successfully modeled using VHDL and the simulation results show that the designs are working well. The VHDL codes are successfully downloaded to the FPGA to perform the open/short test. The design consists of frequency step down module, state machine module, storage module and display module. The total time required to perform the 4 pins open/short test is 3.04615ms.

# REFERENCES

- [1] Mohan, N. & Kumar, A, "Modeling ESD protection", IEEE Potentials, Vol 24, Issue 1, pp. 21-24, Feb-Mar 2005

- [2] Sadiku, M.N.O. & Akujuobi, C.M., "Electrostatic discharge (ESD)", IEEE Potentials, Vol 22, Issue 5, pp. 39-41, Dec 2003

- [3] M. D. Ker; J. J. Peng and H. C. Jiang, <u>ESD test methods on integrated circuits: an overview</u>, The 8th IEEE International Conference on Volume 2, Issue, 2001 Page(s):1011 1014 vol.2, 2001.

- [4] M.-D. Ker, "Whole-chip ESD protection design with efficient VDD-to-VSS ESD clamp circuits for submicron CMOS VLSI," *IEEE Trans. on Electron Devices*, vol. 46, pp. 173-183, 1999.

- [5] J.M. Rabaey, A. Chandrakasan and B. Nikolic, Digital Integrated Circuits: A Design Perspective (2<sup>nd</sup> Ed.), Prentice Hall, 2003.