# An efficient nonstationary Wiener filter hardware implementation

Veselin N. Ivanović, Srdjan Jovanovski

Abstract—An efficient multicycle hardware design of a nonstationary (time-varying (TV)) Wiener filter, based on timefrequency (TF) analysis, is considered. It is developed by following the idea of a new method for filter's region of support (FRS) realtame estimation, also proposed here. Quite general estimation method, based on cross-terms-free time-frequency representations (TFDs), provides multiple detection of the local filter's regions of support (in observed time-instant) in the practically only important case of a known single noisy signal realization. In this way, a very efficient real-time filtering of mono- and multicomponent nonstationary signals is enabled. Designed multicycle hardware design, required by the proposed estimation method, allows the implemented nonstationary Wiener filter to take different number of clock cycles per frequency point and to share functional kernels (that executes the TF representation) within the execution. In this way, (i) the application of the commonly used TFDs in the nonstationary filtering area, (ii) the optimization of the critical design performances (hardware complexity, energy consumption and cost) and (iii) the execution time improvement are provided.

**Keywords**—Time-varying filtering; Region of support; Instantaneous frequency; Estimation; Time-frequency distributions; Hardware implementation; FPGA devices.

## I. INTRODUCTION

Efficient processing of nonstationary signals, including their filtering, requires a TV approach, allowing TV filtering to benefit from the TF analysis results. The TF analysis based nonstationary filtering has been dealt with only in a few papers, [1]–[9]. This solution, applied to the case of a known single noisy signal realization (common and practically the only important case, treated in this paper), reduces nonstationary filtering problem to the summation of the frequency-only-dependent short-time Fourier transform (STFT) samples from the estimated filter's region of support. This significantly simplifies the TV filtering execution, making it very attractive for implementation. However, the implementations, based on the STFT one and the quite complex filter's region of support detection, [3], [10], are

Manuscript received January 15, 2008: Revised version received July 29, 2008. This work was supported by the Ministry of Education and Science of the Republic of Montenegro..

V. N. Ivanović is with the University of Montenegro, Department of Electrical Engineering, 81000 Podgorica, MONTENEGRO (phone: +382 67 331 866; fax: +381 20 245 873; e-mail: very@cg.ac.yu).

S. Jovanovski is with the University of Montenegro, Department of Electrical Engineering, 81000 Podgorica, MONTENEGRO (e-mail: srdjaj@cg.ac.yu).

quite numerically and time consuming, that seriously restrict nonstationary filtering applications in real-time. In practice, the nonstationary filter hardware implementation, if possible, can overcome this nuisance.

Although challenging and practically very important, the nonstationary filtering implementation approaches are so far considered only in a few papers, [3], [10]. Recognizing the existing implementation methods, [3], [10], as unsuitable for the nonstationary signals filtering in real-time, in Section III we propose a new FRS estimation method and develop (in Section V) a TV filter's real-time design based on it. The significance of the proposed nonstationary Wiener filter hardware design is investigated in Section VI.

#### II. THEORY

The Wigner distribution (WD) based nonstationary filtering, defined by using Weyl correspondence, [1]–[3], that overcomes distortion of the filtered signal (Hx)(n), is, [3]:

$$(Hx)(n) = \sum_{k=-N/2+1}^{N/2} L_H(n,k)STFT_x(n,k).$$

(1)

$L_H(n,k)$  is the Weyl symbol for the FRS,  $STFT_x(n,k)=DFT_m\{w(m)x(n+m)\}$  is the STFT of the nontationary, m-component noisy FM signal.

$$x(n) = f(n) + \varepsilon(n) = \sum_{i=1}^{m} f_i(n) + \varepsilon(n), \qquad (2)$$

w(m) is the real-valued lag window and N is the signal duration. Note that, based on (1), the nonstationary filtering, in the observed time-instant, can be performed by determining filter's region of support and by summing the corresponding frequency-only-dependent STFT samples from the determined region. Following the procedure for the Wiener filter design (from the stationary signals case, [11]), in the case of uncorrelated original nonstationary signal and additive noise, region of support of the nonstationary Wiener filter can be easily reduced to the form, [5], [6]:

$$L_{H}(n,k) = 1 - \frac{WS_{\varepsilon}(n,k)}{WS_{x}(n,k)},$$

(3)

where  $WS(n,k) = E\{WD(n,k)\}$  represents Wigner spectrum (WS) and  $WS_{f\varepsilon}(n,k) = 0$ , [12]. Knowing that WS highly concentrate energy of the considered FM signals  $f_i(n)$ , i=1,...,q around their instantaneous frequencies (IFs),  $IF_i(n)$ , i=1,...,q (without cross-terms presence), [12], [13], as well as that the considered white noise is widely spread in the TF

plane [3], [12], [13], it can be easily concluded that only a small part of noise, that can be neglected with respect to the rest of noise energy, lies around the  $IF_i(n)$ , i=1,...,q. Consequently, based on (3), filter's region of support, satisfying these requirements, corresponds to the IF of the original multicomponent signal, [3], [6]. In this way, the FRS determination problem is reduced to the IF estimation in a noisy environment, here named the IF/FRS estimation.

In practice, the nonstationary signals filtering (and, consequently, the IF/FRS estimation) should be performed on a single noisy signal realization. This makes the WS usage impossible and requires its approximation by an appropriate cross-terms-free TFD that additionally provides high quality IF/FRS estimation in the nonstationary signals case. Consequently, by applying the TF analysis solution, the IF/FRS estimation is reduced to determination of the frequency points where TFD of noisy signal has local maxima in observed time-instant n,

$$IF_i(n) = \arg[\max_{k \in Q_{k_i}} TFD_x(n, k)], \tag{4}$$

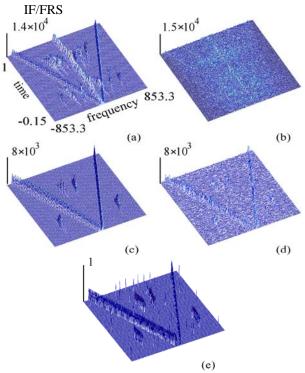

where  $Q_{k_i}$  is the frequency interval around the *i*-th signal component, whose IF is  $IF_i(n)$ , [14]–[16]. Since, among the quadratic TFDs, the WD produces the best IF/FRS estimation characteristics in the highly nonstationary signals case, [15] and, simultaneously, exhibits serious drawbacks in the multicomponent signals analysis, [13], [17], Fig.2(a),(b), alias- and cross-terms-free WD, named S-method (SM), [17], Fig.2(c), is proposed as an appropriate IF estimator, [15], [16]. It retains the desired characteristics of the WD-based IF/FRS estimator, from the monocomponent signals case, and removes its disadvantages, from the multicomponent signals case, [16]. Precisely, in the non-overlapping multicomponent signals cases, the SM-based IF/FRS estimation characteristics, obtained for each signal's component separately, remain the same as in the case when only that particular component exists. Additionally, these results significantly outperform the results obtained by the spectrogram (SPEC), [16], and, consequently, by the other reduced interference TFDs, [15], [16]. Furthermore, by the definition, [17],

$$SM_{X}(n,k) = \left| STFT_{X}(n,k) \right|^{2}$$

$$+2\operatorname{Re}\left\{ \sum_{i=1}^{L} STFT_{X}(n,k+i)STFT_{X}^{*}(n,k-i) \right\}$$

(5)

the SM implementation uses the STFT samples, included in the TV filtering definition (1), as well. In (5), 2L+1 is the rectangular convolution window width, introduced to make the SM with the WD representation quality. In the real-valued analyzed signals case, the imaginary parts of the STFT vanish in (1),

$$(Hx)(n) = \sum_{k=-N/2+1}^{N/2} L_H(n,k) \operatorname{Re} \{STFT_X(n,k)\}$$

(6)

since, in that case,  $SM_x(n,-k)=SM_x*(n,k)$  holds and, then, the FRS becomes a symmetric function in frequency.

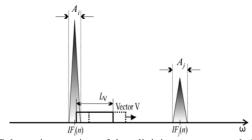

Fig. 1: Schematic overview of the adjoining auto-terms, their widths and mutually distance that determine the sliding vector size.

### III. REAL-TIME IF/FRS ESTIMATION METHOD

A method, capable of providing the required IF/FRS estimation in real-time, should: (1) be computationally simple enough to enable real-time implementation, (2) be signal independent to enable all local maxima detection (in observed time-instant) in the multicomponent signals case, (3) produce high quality estimation (with minimal possible and noise-only-dependent estimation error).

Before introducing the new IF/FRS estimation method, consider first the existing ones, [3], [10], against the above requirements. The computational method from [3] is based on two TFDs, with extremely different numbers of samples of the filtered signal, and on a specific statistics approach of comparing their biases and variances. In that way, it requires post-processing of the filtered signals and computationally complex and highly time consuming IF/FRS detection, so it is useless for real-time implementation (requirement (1)). The real-time method from [10], based on the global TFD maximum detection, being highly signal dependent (see Section VI), is unsuitable in the multicomponent signals case (requirements (2), (3)).

Following and satisfying requirements (1)–(3) in observed time-instant, we propose application of the sliding vector V over frequency-only-dependent samples of the high quality, cross-terms-free, TFD based IF estimator. The frequency point that corresponds to the maximal vector element is recognized as a local IF/FRS, but only if the maximal vector element is both: (I) the central one, and (II) greater than the introduced spectral floor.

In this way, each new TFD sample, imported in the vector V area, causes vector sliding for one position, enabling local IF/FRS detection for the next frequency point in real-time (requirement (1)). At the same time, under condition (I) and by limiting the sliding vector size  $(L_V)$  by

$$L_{V} \ge L_{V,\min} = 2 \times \max_{1 \le i \le q} \{A_{i}\}$$

(7)

$(A_i, i=1,2,...,q)$  are the different widths of the supposed non-overlapping auto-terms, Fig. 1), satisfying requirement (3), the method provides that:

For each time instant, all frequency points from the observed auto-term, including the true IF, have the corresponding TFD samples inside the sliding vector when the IF/FRS is detected. Then, the noise-onlydependent IF/FRS estimation error is produced inside the auto-terms' domains, making high quality

Fig. 2: (a) WD of (4); (b) WD of noisy signal (4); (c) SM of (4); (d) SM of noisy signal (4), (e) FRS estimated by applying proposed estimation method on the SM from (d).

estimation inside these domains;

- For each signal component and each time instant, only one  $L_H(n,k)$  value can assume value 1, so that, based on discussion from [3], the influences of the frequency discretization and of the true IF/FRS position between the grid points on the estimation quality are reduced. Additionally, in this way, the possible negative influence of the unequal widths of the filter's regions of support (in different time-instants) on the output signal quality is avoided.

Simultaneously, under condition (I), but by limiting the sliding vector size by

$$L_V < L_{V,\text{max}} = 2 \times \min_{1 \le i, j \le a, i \ne j} |IF_i(n) - IF_j(n)|$$

(8)

the possibility of masking the local TFD maximum by the adjacent (possible higher) ones is avoided, Fig.1. In this way, satisfying requirement (2), the IF/FRS estimation in the multicomponent signals case is provided.

Since the TFD based estimators highly concentrate signals energy ( $L_{V, \rm min} \ll L_{V, \rm max}$  in the non-overlapping signal's components case, [13], [17]), the conclusion about robustness of this method with respect to the sliding vector size can be easily derived (and experimentally proved), as long as it takes values from the usually wide frequency range of  $[L_{V, \rm min}, L_{V, \rm max}]$ . However, from the implementation point of view, smaller  $L_V$  could improve execution time and reduce calculation complexity.

Note that the described conditions of the estimation method can be satisfied outside the auto-terms too – in the frequency

points that contribute to the output noise energy only. To

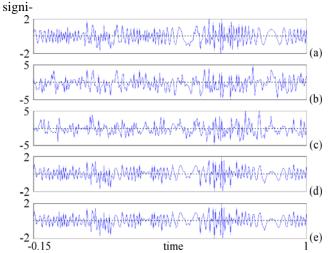

Fig. 3: (a) Signal *f*(*t*); (b) Noisy signal; (c) Noisy signal filtered by using the time-invariant filter with the cutoff frequency equal to the maximal signal frequency; (d) Noisy signal filtered numerically by using the FRS from Fig.2(e); (e) Noisy signal filtered by using proposed real-time design, implemented in FPGA devices.

ficantly suppress this effect, the estimation method compares each recognized IF/FRS point with the introduced spectral floor R, defined as a fraction of the maximal TFD value. Although greater spectral floor values would almost eliminate noise influence outside the auto-terms, they can produce significant edge cutting of the finite duration auto-terms (such as in the chirp signals case). After the numerous experiments, we concluded that the spectral floor values of the (10-25)% of the maximal TFD value are suitable in most practical applications.

#### IV. EXAMPLE

Real-valued, multicomponent, highly nonstationary signal f(t) (with almost full frequency range second component, Fig.2(a), whose normalized signal rate is 0.85) is observed on the interval -0.15 to 1

$$f(t) = e^{-100(t-10/16)^2} \cos(840(t-1/5)^2) +$$

$$+ e^{-0.5(t-9/16)^2} \cos(2000(t+1/5)^2) +$$

$$+ e^{-100(t-1/8)^2} \cos(325(t+5)^2),$$

(9)

where  $t=nT_w/N$ . It is masked by the high white noise such that  $SNR_{in}=10\log(P_f/P_\epsilon)=-1.7238[dB]$ , Fig.3(b). TV filtering, based on the proposed method, is done. The Hanning lag window width of  $T_w=0.15$ , the sliding vector size of  $L_V=11$ , and L=3,  $R=0.2\times\max_{n,k}\{SM_x(n,k)\}$ , N=256 are applied. Neglecting the noted discretization effects, we obtain very high improvement,  $SNR_{out}=17.85[dB]$ , Fig.3(c),(d). Note that it can theoretically be approximately up to  $(A/N)\times 10\log(N/4)+(B/N)\times 10\log(N/2)=20.1[dB]$  in a partly 2-component (in the B=173 time instants) and a partly 4-component (in the A=83 time instants) signal case. Due to the discretization effects, we cannot get so high improvements.

However, regardless these effects, obtained improvements are still rather very high (see Fig. 3(d),(e)). On the other From STFT Module FIFO delay STFTRe(n,k)STFTRe(n,k+L+1)STFTRe(n, k-1)(Hx)(n) $0 \longrightarrow \overline{\text{STFTRe}(n, \underline{k} + L)}$ ConvWinRegBlk CumADD CkRESET CLK Store (LV-1)/2 STFTRe(n,k-(LV-1)/2)CumADD STFTRe(n,k)CumADD STFT-to-SM (Hx)SM/STFT Store u Gateway SMx(n,k)**ADD** 0 0 2L STFTRe $(\underline{n,k-L})$ 1,2 SC SMx(n,k)ShLorNo 0 Start\_Filtering SelSTFT Ð FD RESET SMx(n,k-1)Control logic for From STFT Module Max Freq STFT Load filtering execution STFTIm(n,k+L+1)**EOF** Freq\_Border and FΒ  $0 \longrightarrow \overline{\text{STFTIm}(n, k+L)}$ padding borders End Process COMP (L|V-1)/2CLK SMx(n,k-(LV-1)/2)R **CLK** SM Store CumADD CLK STFTIm(n,k)STFT-to-SM STFT Load RESET CLKs and RESETs Gateway signals Control SMx(n,k-(LV-2))(Hx) Store l-bits Freq Border SMx(n,k-(LV-1))1,2 CumADD RESET STFTIm(n,k-L)Store ShMemBuff SelSTFT ShLorNo RESET Control Logic SM/STFT RESET Configuration Reg. SelSTFT 1 BinCount SelSTFT 2 SVS CLK SC ShLorNo SM/STFT\_Store TFDCode FD Din FΒ CLK Config. Signals System STFT Load **CWS** CLK (from PC or MC CumADD CLK **SVS** STFT samples from EOF STFT-to-SM Gateway ConvWinRegBlk SM/STFT\_Store MUX1 ShLEFT CumADD Address RESET SelSTFT Freq Border Enable (EN) SelSTFT 1 SelSTFT 2 SM(n,k)STFT Load (Hx) Store ShLorNo ShLorNo MUX2 **CLK** CumADD RESET Max Freq inv(CLK) RESET SelSTFT 2 RESET CLKs and RESETs signals Control

hand.

Fig. 4: Proposed hardware design of the nonstationary Wiener filter.

since the signal (9) occupies almost full frequency range, [-760 to 766.7] Hz of the full frequency range [-853.3 to 853.3] Hz, Fig. 2(c), its conventional time-invariant filtering would produce a weak improvement. For example, the timeinvariant filter with cutoff frequency equal to the maximal signal frequency, Fig. 3(c), would theoretically produce improvement of  $10\log(N/231)=0.45[dB]$ .

V. NONSTATIONARY WIENER FILTER HARDWARE DESIGN Architecture for the real-time nonstationary Wiener filter design, based on the proposed estimation method, is given in

Fig.4. STFT-to-SM gateways and convolution window registers blocks (ConvWinRegBlks), used in pairs, implement, based on (5), the SM real and imaginary computational lines in L+1 CLKs (the details can be found in [18], [19]). In the next two cycles the TV filter function is implemented. By setting SM/STFT\_Store signal in (L+1)-st cycle, the computed SM and the corresponding STFT<sub>Re</sub> samples are stored in the shift memory buffer (ShMemBuff) and in the FIFO delay, respectively. ShMemBuff implements the sliding vector function. FIFO delay block delays STFT samples, so the FIFO delay output sample corresponds (in frequency) to the ShMemBuff central element (ShMemBuff[ $(L_V-1)/2$ ]). The ConvWinRegBlks and ShMemBuff, implemented as arrays of parallel-in-parallel-out registers, determine time and address order of their elements by each *STFTLoad* and

*SM/STFT\_Store* cycle, respectively. The set of comparators,

Table I: LUT's values for given L. The ADD(STFT<sub>M</sub>) means the address location of the middle ConvWinRegBlk element. Symbol << denotes logical shift left operation and l=CEIL(log<sub>2</sub>N)=Length(SelSTFT\_1).

| LUT's memory | Control signals area |               |           | Gateway MUXs' addresses |                   |

|--------------|----------------------|---------------|-----------|-------------------------|-------------------|

| location     | ShLorN               | SM/STFT_Store | STFT_Load | SelSTFT_1               | SelSTFT_2         |

| 0            | 0                    | 0             | 0         | ADD/CEPTE ) I           | ADD/CEET )        |

| Ü            | 0                    | 0             | 0         | $ADD(STFT_M) << l$      | $ADD(STFT_{M})$   |

| 1            | 1                    | 0             | 0         | $ADD(STFT_{M+1}) << l$  | $ADD(STFT_{M-1})$ |

|              | 1                    | 0             | 0         |                         |                   |

| L            | 1                    | 0             | 0         | $ADD(STFT_{M+L}) << l$  | $ADD(STFT_{M-L})$ |

| L+1          | 0                    | 1             | 0         | 0                       | 0                 |

| L+2          | 0                    | 0             | 1         | 0                       | 0                 |

Table II: Parameters, from "Configuration registers", expressed by the number of needed STFT\_Load cycles.

| Configuration register    | Parameter specified and its description                      | Parameter's value |

|---------------------------|--------------------------------------------------------------|-------------------|

| Start Convolution (SC)    | Start of the SM convolution window operation                 | (2L+1)-1          |

| Filtering/FIFO Delay (FD) | Delay (in frequency) for the FRS estimation/STFT propagation | $(L_V-1)/2+1$     |

| Frequency Border (FB)     | Frequency border position                                    | N-L-1             |

| Conv. Win. Size (CWS)     | Size of convolution window                                   | 2L+1              |

| Sliding Vector Size (SVS) | Size of the sliding vector V                                 | $L_V$             |

| End of Filtering (EOF)    | End of filtering process                                     | $N \times N - 1$  |

represented as COMP block, determines local FRS by generating  $C_k$  signal.  $C_k$ =1, produced when ShMemBuff[ $(L_V$ -1)/2] $\geq R$  is the maximal ShMemBuff element, enables participation of the FIFO delay output sample in the output signal generation. Cumulative adder (CumADD) sums the STFT samples, from the FRS, with the latency of half of the CLK cycle regarding the  $SM/STFT\_Store$  signal. By setting  $STFT\_Load$  signal in (L+2)-nd cycle, the new STFT sample is imported. After that, described process is repeated for the next frequency point. In parallel, but only when maximal frequency SM sample becomes central ShMemBuff element (detected by the  $Max\_freq$  signal), the computed (Hx)(n) value is stored into the output register. With a latency of half of the CLK cycle, the CumADD is reset and the (Hx)(n) calculation, for the next time instant, may begin.

Look-up-table (LUT), Table I, manages the execution. The binary counter generates its low addresses, while *L* from TFDCode register sets the high ones. Operations at the maximal frequency are managed by *Start\_Filtering*, *Max\_Freq*, *Freq\_Border* and *End\_Process* signals. They are generated, by considering the synchronization conditions related to the *CLK* and *STFT\_Load* cycles, in the modules whose basic components are variable length up-down binary counters (with asynchronous reset) and binary magnitude comparators (their binary references are stored in the "Configuration registers", Table II). Note that *Freq\_Border* signal is generated to reset the gateways, allowing to pad the frequency border with 2*L* 0's.

Note that proposed design enables application of various TFDs in the TV filtering research area, in different number of CLKs: the spectrogram application (for L=0), the SM

application, up to the WD application (for maximal L=(N-1)/2). The system with L=0 has minimal time requirements (3 CLKs by frequency point). But, the IF/FRS estimation quality is improved with incrementing L, [16]. Consequently, we propose application of the SM with small L (L=2, 3), since they give very high IF/FRS estimation quality and have the satisfactory time requirements (5, 6 CLKs by frequency point). Opposite to the possible single-cycle implementation, the proposed design allows sharing of the functional units (STFT-to-SM gateways) within the execution, so it optimizes design performances (see Section VI) giving one the possibility to implement nonstationary Wiener filter by using standard devices. We have verified the proposed architecture by an FPGA chip real-time design. Here we give only the FPGA device output, Fig.3(d).

#### VI. PROPOSED HADRWARE DESIGN SIGNIFICANCE

Finally, we will compare proposed hardware design with the other filtering implementation solutions: existing (timeinvariant and single-cycle) ones and possible (hybrid) one.

TV approaches produce importantly greater noisy reduction in the nonstationary signals case regarding the conventional, time-invariant, filtering approaches. Precisely, TV approaches produce up to the  $10\log(B)$  greater improvement over the time-invariant ones, where B denotes frequency range that occupy filtered nonstationary signal. Additionally, the improvement gain increases as frequency range increases, achieving significant value in the case of highly nonstationary filtered signals (signals that occupy high frequency range, see Example from Section IV). This reason is more that sufficient for the interest in the TV approaches implementation in the

nonstationary signals case.

In the observed time-instant and the considered frequency point, single-cycle approaches, such is one proposed in [10], execute TV filtering in one CLK cycle. This means that at the end of each CLK cycle, the corresponding frequency point must be recognized as the IF or not, without possibility of comparing of its corresponding TFD value with the TFD values in the near-by points. Precisely, TFD maximum detecti-

Table III: Total number of functional units in the STFT-to-SM gateway and corresponding clock cycle time and execution time in the cases of proposed multicycle design (MCI) and possible hybrid approach. The SM with arbitrary L is considered.  $T_m$  is the multiplication time of a two-input l-bit multiplier,  $T_a$  is the addition time of an l-bit two-input adder, whereas  $T_s$  is the 1-bit shift time. The recursive form of the STFT module implementation is assumed when the clock cycle time in the possible hybrid case is calculated.

| Approach     | Adder<br>s | Multipliers | Shift left registers | Clock cycle time        | Execution time                |  |

|--------------|------------|-------------|----------------------|-------------------------|-------------------------------|--|

| Hybrid       | L          | L+1         | L                    | $2T_m + (L+3)T_a + T_s$ | $6T_m + 3(L+3)T_a + 3T_s$     |  |

| Proposed MCI | 1          | 1           | 1                    | $T_m + 2T_a + T_s$      | $(L+3)T_m+2(L+3)T_a+(L+3)T_a$ |  |

on must be performed from the global TF level, by comparing each calculated TFD value (from the corresponding CLK cycle) with the global maximum spectral value, which must be highly dependent on the global maximum of the filtered signal. This fact disables local TFD maxima detection, making single-cycle approaches highly signal dependent and, consequently, unusable in the cases of the multicomponent signals. Also, due to the possible auto-terms edge cutting, these approaches are unusable in the case of finite duration FM signals (such as the chirp signals). Additionally, even in the monocomponent signals case, due to the high noise influence, the global maximum TFD detection based approaches give unequal widths of the filter's regions of support in different time-instants, that negatively influence the output signal quality, [3].

Possible hybrid implementation approach, based on the single-cycle implementation of the SM, could follow the proposed estimation method and, then, could allow (in the next two cycles) local TFD maxima detection and appropriate TV filtering of the multicomponent signals in real-time. Consequently, this approach can be compared with the proposed multicycle one. Comparison of the architectures' resources used in the hybrid architecture and in the proposed multicycle one, as well as comparison of their clock cycle times and the execution times are given in Table III. The following advantages of the proposed multicycle approach can be noted:

- Required reduction of the hardware complexity is achieved by sharing functional kernels, named as STFT-to-SM gateways (precisely, it is achieved by introducing the pair of multiplexers at the gateway's input, as well as the gateways' CumADDs, instead of the conventional adders). The achieved hardware reduction is significant, and it increases as the SM convolution window width (L) increases;

- Since the introduced multiplexers are fairly small, this could yield a substantial reduction in the hardware cost and energy consumptions, as well as in the used chip dimensions, [19];

- The clock cycle time in the multicycle design is much shorter. Additionally, hybrid approach could not

- succeed to balance the amount of work done in each CLK cycle, since the SM implementation (from the first CLK cycle) determines it;

- Significantly improved execution time in the multicycle implementation approach case can be achieved. Precisely, regarding the technology limitations of the used implementation units (adders, multipliers, shift registers), it can be easily calculated that the proposed multicycle approach execution time reduces the hybrid approach execution time, as long as *L*<6. Note that this property has a great practical significance, since the SMs with small *L* (*L*≤3) are usually used, when the execution times in the considered cases are differ significantly.

Finally the ability to enable application of the almost all commonly used TFDs (SPEC, WD, SM with arbitrary L) in the nonstationary filtering research area by the same hardware design represents an additional advantage of the proposed multicycle design.

# VII. CONCLUSION

A flexible real-time implementation of the TF analysis based TV filtering system is developed by following the idea of a method for the filter's region of support real-time estimation, also proposed here. Simple estimation method enables high quality filtering of the nonstationary multicomponent signals in real-time. Proposed multicycle design enables application of various commonly used TFDs in the TV filtering area, allowing practical verification by designing FPGA chip, capable of performing the real-time nonstationary filtering. Moreover, it significantly improves other approaches (existing time-invariant and single-cycle ones, as well as the possible hybrid one) regarding usual comparative criteria, such as calculation speed, hardware complexity, power consumption and cost.

## REFERENCES

G. Matz, F. Hlawatsch, W. Kozek: "Generalized evolutionary spectral analysis and the Weyl spectrum of nonstationary random processes," *IEEE Trans. SP*, vol.45, no.6, pp.1520-1534, June 1997.

- [2] R.G. Shenoy, T.W. Parks: "The Weyl correspondence and time-frequency analysis," *IEEE Trans. on SP*, vol. 42, no. 2, pp. 318-331, Feb.1994.

- [3] LJ. Stanković: "On the time-frequency analysis based filtering," *Ann. Telecomm.*, vol.55, no.5/6, pp.216-225, May/June 2000.

- [4] G.F. Boudreaux-Burtels, T.W. Parks, "Time-varying filtering and signal estimation using Wigner distribution," *IEEE Trans. on Acoust., Speech, Signal Processing*, vol. 34, no. 6, pp. 442-451, 1986.

- [5] A. J. E. M. Jannssen, "Wigner weight functions and Weyl symbols of nonnegative definite linear operators," *Phillips J. Research*, vol. 44, pp. 7-42, 1989.

- [6] W. Kozek, "Time-frequency processing based on the Wigner-Weyl framework," *Signal Processing*, vol. 29, no. 10, pp. 77-92, 1992.

- [7] A. W. Rihaczek: "Signal energy distribution in time and frequency," IEEE Trans. Information Theory, vol.14, pp. 369-374, 1968.

- [8] R. G. Shenoy, T. W. Parks, "The Weyl correspondence and time-frequency analysis," *IEEE Trans. on Signal Processing*, vol. 42, no. 2, pp. 318-331, 1994.

- [9] L. A. Zadeh, "Frequency analysis of variable networks," *Proceedings IRE*, vol. 67, pp. 291-297, 1950.

- [10] S. Stanković, LJ. Stanković, V. N. Ivanović, and R. Stojanović: "An architecture for the VLSI design of systems for time-frequency analysis and time-varying filtering," Ann. Telecomm., vol. 57, no. 9-10, 2002, pp. 974-995.

- [11] A. Papoulis, Signal analysis, McGraw Hill Company, New York, 1977.

- [12] P. Flandrin, W. Martin, "The Wigner-Ville spectrum of nonstationary random signals," in *The Wigner distribution: Theory and applications in signal processing, Eds. W.Mecklenbrauker, F.Hlawatch*, pp.211-267.

- [13] L. Cohen, Time-frequency analysis, Prentice Hall, 1995.

- [14] B. Boashash: "Estimating and interpreting the instantaneous frequency of a signal – Part 1: Fundamentals", *Proc. IEEE*, vol. 80, no. 4, 1992, pp. 519-538.

- [15] V. N. Ivanović, M. Daković, LJ. Stanković: "Performances of quadratic time-frequency distributions as instantaneous frequency estimators," *IEEE Trans. SP*, vol.51, no.1, Jan.2003, pp.77-89.

- [16] M. Daković, V. N. Ivanović, LJ. Stanković: "On the S-method based instantaneous frequency estimation," in *Proc. 7th Int. Symp. on Signal Processing and its Applications*, Paris, France, July 01-04, 2003.

- [17] LJ. Stanković: "A method for time-frequency analysis," *IEEE Trans. SP*, vol.42, pp.225-229, Jan.1994.

- [18] V. N. Ivanović, R. Stojanović, LJ. Stanković: "Multiple clock cycle architecture for the VLSI design of a system for time-frequency analysis," EURASIP J on Appl. Sign. Proc., Spec. Iss. Design Methods for DSP Syst., 2006, pp. 1-18.

- [19] V. N. Ivanović, R. Stojanović: "An efficient hardware design of the flexible 2-D system for space/spatial-frequency signal analysis", *IEEE Trans. SP*, vol. 55, no. 6, June 2007, pp. 3116-3125.

Veselin N. Ivanović was born in Cetinje, Montenegro, April 10, 1970. He received the B.S. degree in electrical engineering, 1993, and the M.S. degree in electrical engineering from the University of Montenegro, 1996. He received the Ph.D. degree in electrical engineering from the same university, 2001, in time-frequency signal analysis and architecture design for implementation of time-frequency methods and time-varying filtering. In 2001, he received the Siemens Award for scientific achievements in his Ph.D.

He is a Professor at the Electrical Engineering Department, University of Montenegro. During the period of 2002–2006, he was Vice Dean at the Electrical Engineering Department, University of Montenegro. His research interests are in the areas of time-frequency signal analysis, design of the special purpose architectures for signal processing, hardware/software codesign, computer organization and design, and design with microcontrollers.

Prof Ivanović is a member of the IEEE, EURASIP and WSEAS.

**Srdjan Jovanovski** was born in Bar, Montenegro, August 30, 1982. He received the B.S. degree in electrical engineering, 2005, and the M.S. degree in electrical engineering from the University of Montenegro, 2006.

He is a Ph.D. student at the Electrical Engineering Department, University of Montenegro. His research interests are in the areas of time-frequency signal analysis, and design of the special purpose architectures for signal processing.